# FIUBA

# (86.03) DISPOSITIVOS SEMICONDUCTORES Carpeta

Rocío Perroni 1er cuatrimestre 2020

# Índice

| 1.         | Físi | ca de Semiconductores                         | 1        |

|------------|------|-----------------------------------------------|----------|

|            | 1.1. | Modelo de bandas de energía                   | 1        |

|            | 1.2. | Equilibrio térmico                            | 2        |

|            | 1.3. | Semiconductores extrínsecos                   | 3        |

|            | 1.4. | Mecanismos de conducción                      | 4        |

|            |      | 1.4.1. Movilidad de portadores                | 4        |

|            |      | 1.4.2. Densidad de corriente de arrastre      | 5        |

|            |      | 1.4.3. Densidad de corriente de difusión      | 7        |

| •          | T-1  |                                               | _        |

| 2.         |      |                                               | 8        |

|            |      | Densidad de carga espacial $\rho$             | 8        |

|            | 2.2. |                                               | 8        |

|            | 2.3. | Potencial electrostático o de built-in $\phi$ | 8        |

|            | 0.4  | 2.3.1. Regla de los 60 mV                     | 8        |

|            | 2.4. | Aproximación de cuasi-neutralidad             | 8        |

|            | 2.5. | Relación de Boltzman                          | 8        |

| 3.         | Jun  | tura PN                                       | .0       |

|            | 3.1. | Aproximación de vaciamiento                   | 10       |

|            |      | 3.1.1. Casos de interés                       | 12       |

|            | 3.2. |                                               | 13       |

|            | 3.3. |                                               | 15       |

|            | 3.4. | Diagrama de bandas de energía                 | 15       |

| 1          | D:a  | do PN                                         | .6       |

| 4.         | 4.1. |                                               | . o      |

|            |      | v                                             |          |

|            | 4.2. | •                                             | 18<br>10 |

|            | 4.3. |                                               | 18       |

|            | 4.4. | <u></u>                                       | 18       |

|            | 4 5  | 1 1                                           | 19       |

|            | 4.5. |                                               | 20       |

|            |      |                                               | 20       |

|            |      | 9                                             | 21       |

|            | 4.0  |                                               | 21       |

|            | 4.6. | 1                                             | 21       |

|            | 4.7. | Diodo Zener                                   | 21       |

| <b>5</b> . | Jun  | tura MOS                                      | 23       |

|            | 5.1. | Regímenes de la juntura MOS                   | 23       |

|            |      |                                               | 24       |

|            |      | 5.1.2. Potencial de banda plana (flatband)    | 24       |

|            |      | · · · · · · · · · · · · · · · · · · ·         | 24       |

|            |      |                                               | 25       |

|            |      |                                               | 25       |

| c          | TD:  | MOCEET                                        |          |

| ο.         |      |                                               | 28<br>20 |

|            |      | <u>.</u>                                      | 29       |

|            | 0.2. | <u>.</u>                                      | 29       |

|            |      | 6.2.1. NMOS                                   | 29       |

|    |      | 6.2.2.   | PMOS                                                | <br> | <br> |  |  | 29 |

|----|------|----------|-----------------------------------------------------|------|------|--|--|----|

|    |      | 6.2.3.   | Corte                                               | <br> | <br> |  |  | 30 |

|    |      | 6.2.4.   | Triodo                                              | <br> | <br> |  |  | 30 |

|    |      | 6.2.5.   | Saturación                                          | <br> | <br> |  |  | 31 |

|    | 6.3. | Efecto   | o de modulación del largo del canal                 | <br> | <br> |  |  | 32 |

|    | 6.4. | Recta    | de carga                                            | <br> | <br> |  |  | 32 |

|    | 6.5. | Pasos    | para resolver circuitos con MOSFET                  | <br> | <br> |  |  | 33 |

|    | 6.6. | Model    | lo de pequeña señal                                 | <br> | <br> |  |  | 34 |

|    |      | 6.6.1.   | Transconductancia $g_m \ldots \ldots \ldots \ldots$ | <br> | <br> |  |  | 34 |

|    |      | 6.6.2.   | Resistencia de salida $r_0$                         | <br> | <br> |  |  | 34 |

|    |      | 6.6.3.   | Transconductancia de $backgate g_{mb}$              | <br> | <br> |  |  | 34 |

|    |      | 6.6.4.   | Capacidad de gate contra canal de inversión         | <br> | <br> |  |  | 35 |

|    |      | 6.6.5.   | Capacidad gate - drain                              | <br> | <br> |  |  | 35 |

|    |      | 6.6.6.   |                                                     |      |      |  |  | 35 |

|    |      | 6.6.7.   | Capacidad body - drain                              | <br> | <br> |  |  | 35 |

|    |      | 6.6.8.   | - · · · · · · · · · · · · · · · · · · ·             |      |      |  |  | 35 |

|    |      |          |                                                     |      |      |  |  |    |

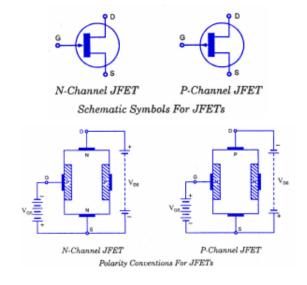

| 7. | Trai |          | r JFET                                              |      |      |  |  | 36 |

|    | 7.1. | Anális   | sis del dispositivo                                 | <br> | <br> |  |  | 36 |

|    | 7.2. | Regim    | nenes del JFET                                      | <br> | <br> |  |  | 38 |

|    | 7.3. | Model    | lo de pequeña señal                                 | <br> | <br> |  |  | 40 |

|    |      |          |                                                     |      |      |  |  |    |

| 8. |      | nsistor  |                                                     |      |      |  |  | 41 |

|    | 8.1. |          | nenes de operación                                  |      |      |  |  | 42 |

|    |      | 8.1.1.   | ,                                                   |      |      |  |  | 43 |

|    |      | 8.1.2.   |                                                     |      |      |  |  | 44 |

|    |      | 8.1.3.   | 0                                                   |      |      |  |  | 45 |

|    |      | 8.1.4.   | 9                                                   |      |      |  |  | 46 |

|    | 8.2. | Model    | lo de Ebers Moll                                    | <br> | <br> |  |  | 47 |

|    | 8.3. |          | lo de pequeña señal                                 |      |      |  |  | 48 |

|    |      | 8.3.1.   |                                                     |      |      |  |  | 48 |

|    |      | 8.3.2.   | Resistencia de entrada                              | <br> | <br> |  |  | 48 |

|    |      | 8.3.3.   | Resistencia de salida                               | <br> | <br> |  |  | 48 |

|    |      | 8.3.4.   | Resistencia de realimentación                       | <br> | <br> |  |  | 48 |

|    |      | 8.3.5.   | Capacidad de carga de la base                       | <br> | <br> |  |  | 48 |

|    | 8.4. | Efecto   | o de modulación del ancho de la base                | <br> | <br> |  |  | 49 |

| _  |      | 11.0     |                                                     |      |      |  |  |    |

| 9. |      | plificac |                                                     |      |      |  |  | 50 |

|    | 9.1. |          | netros de un amplificador                           |      |      |  |  | 50 |

|    |      |          | Ganancia de tensión                                 |      |      |  |  | 50 |

|    |      | 9.1.2.   |                                                     |      |      |  |  | 50 |

|    |      | 9.1.3.   |                                                     |      |      |  |  | 50 |

|    | 9.2. | _        | ificador emisor común                               |      |      |  |  | 51 |

|    |      | 9.2.1.   | 1 (8                                                |      |      |  |  | 52 |

|    |      | 9.2.2.   | Distorsión por alinealidad                          | <br> | <br> |  |  | 52 |

|    |      | 9.2.3.   | 1                                                   |      |      |  |  | 52 |

|    |      | 9.2.4.   | <u> </u>                                            |      |      |  |  | 52 |

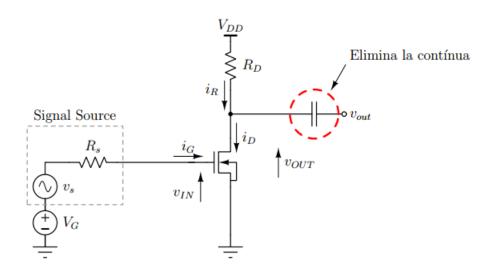

|    | 9.3. | Ampli    | ificador source común                               | <br> | <br> |  |  | 53 |

|    |      | 9.3.1.   | Distorsión por alinealidad                          | <br> | <br> |  |  | 53 |

|    |      | 9.3.2.   | Distorsión por triodo                               |      |      |  |  | 53 |

|    |      | 9.3.3.   | Distorsión por <i>corte</i>                         | <br> | <br> |  |  | 53 |

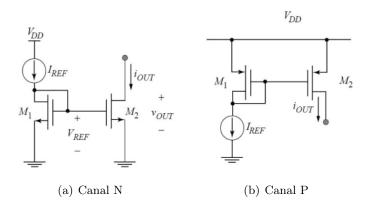

| 9.4. Espejo de corriente con MOSFET                    | 54        |

|--------------------------------------------------------|-----------|

| 10.Dispositivos de potencia                            | <b>55</b> |

| 10.1. Dispositivos no controlados                      | 55        |

| 10.1.1. Diodo Schottky                                 | 56        |

| 10.1.2. Diodos de recuperación rápida                  | 56        |

| 10.1.3. Diodos rectificadores o de frecuencia de línea | 56        |

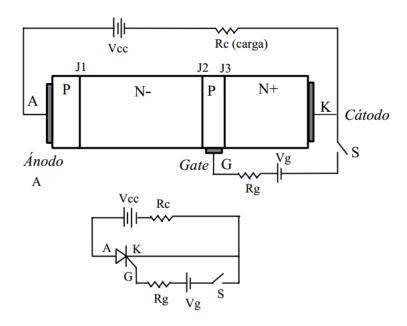

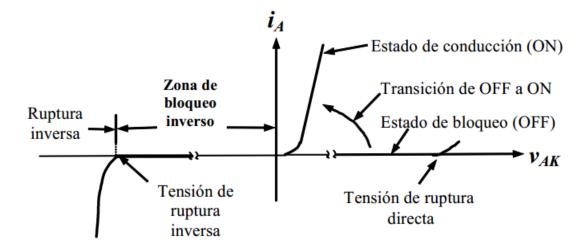

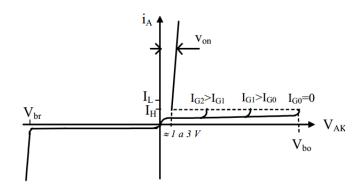

| 10.2. Dispositivos semicontrolados (tiristores)        | 56        |

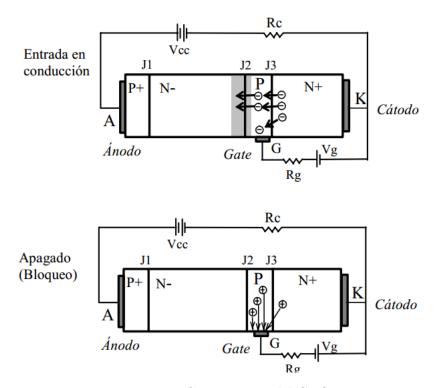

| 10.2.1. SCR: Silicon Controlled Rectifier              | 56        |

| 10.2.2. TRIAC                                          | 59        |

| 10.2.3. GTO: Gate Turn-Off Thyristor                   | 60        |

| 10.3. Dispositivos totalmente controlados              | 61        |

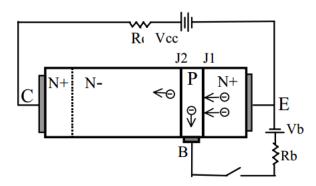

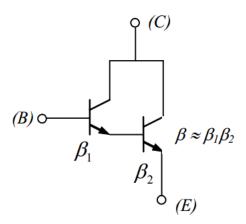

| 10.3.1. Transistor bipolar de potencia                 | 61        |

| 10.3.2. MOSFET                                         | 63        |

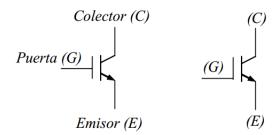

| 10.3.3. IGBT: Insulated Gate Bipolar Transistor        | 63        |

| 10.4. Pérdidas en conducción y conmutación             | 63        |

| 10.5. Comparativa entre dispositivos de frecuencia     | 64        |

| 10.6. Cálculo de disipadores                           | 64        |

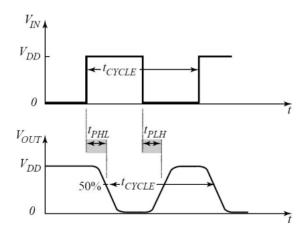

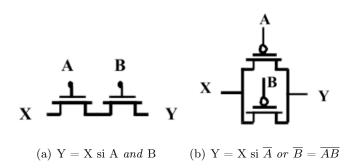

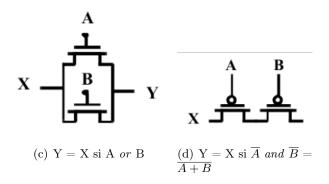

| 11.Circuitos CMOS                                      | 66        |

| 11.1. Tiempo de propagación del inversor CMOS          | 67        |

| 11.2. Complementariedad                                | 68        |

| 11.3. Reglas para síntesis de funciones lógicas        | 69        |

Cursada virtual primer cuatrimestre 2020

#### 1. Física de Semiconductores

Un forma de agrupar a los distintos materiales es a través de la propiedad eléctrica **resistividad**  $\rho$ . Si se mide la corriente I que fluye por una barra de material homogéneo (sección A y largo L) cuando se aplica un voltaje V, se puede encontrar su resistencia R = V/I, la cual se relaciona con la resistividad:

$$R = \rho \cdot \frac{L}{A} \tag{1.1}$$

La resistividad depende de la temperatura. En los materiales semiconductores tiene gran importancia eléctrica, debido a que puede hacerse variar bajo un control muy preciso.

## 1.1. Modelo de bandas de energía

En este modelo de bandas, los electrones no están asociados con ningún núcleo, sino que solo están confinados por las fronteras del cristal. La diferencia entre los números de electrones dentro de las bandas de energía de sólidos diferentes ejerce una fuerte influencia sobre sus propiedades eléctricas.

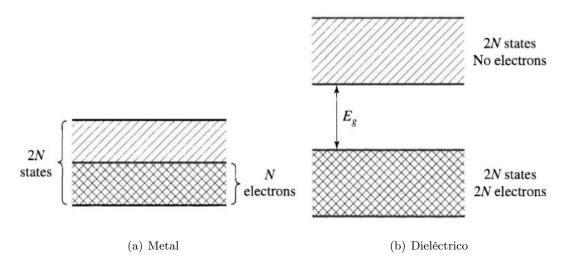

Figura 1.1: Modelos de bandas de energía

- (a) metal (M) compuesto por N átomos, cada uno con un electrón de valencia en la capa externa. En el caso más sencillo la última banda ocupada tendrá 2N estados de los cuales solo estarán ocupados la mitad. Los electrones cerca de la parte superior pueden moverse hacia los estados vacíos sin necesidad de mucha energía (electrones cuasi-libres).

- (b) material dieléctrico (O) de N átomos donde los electrones de valencia llenan por completo una banda. En este caso, los electrones necesitan para moverse una energía mucho mayor a kT/q. Deben superar Eg que, generalmente, es >5 eV (en el SiO2 es aprox. de 9 eV).

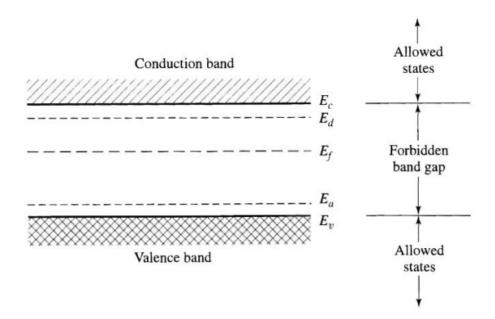

Los semiconductores (SC) tienen estructuras de banda semejantes a los O. La diferencia está en el tamaño de  $E_g$  (del orden 1 eV) y en la capacidad de poblar una banda casi vacía agregando impurezas  $(E_d \ y \ E_a)$ .

El nivel inferior de la banda prohibida (donde no hay estados disponibles) se denomina  $E_v$ , y el nivel superior se denomina  $E_c$ . La diferencia entre ambos se denomina  $E_g$  y es la energía requerida por un electrón para pasar de la banda de valencia a la banda de conducción. El nivel de energía para el

Figura 1.2: Modelo de bandas de energía en un semiconductor

cual la probabilidad de ocupación es de 0.5 se denomina "Nivel de Fermi" y se denota  $E_f$ . Este nivel de energía depende de las masas efectivas de los electrones y en el caso del silicio sin impurezas se halla aproximadamente en la mitad de la banda prohibida. Los electrones por debajo de la banda de valencia están sólidamente vinculados a la red cristalina y no pueden moverse. Los electrones en la banda de conducción pueden moverse.

#### 1.2. Equilibrio térmico

La red cristalina se denomina *ideal* cuando no hay ninguna impureza; en tal caso, al silicio se lo denomina **intrínseco**. A T=0 K la última banda ocupada está llena (banda de valencia BV). Para T >0K, la BV no está completamente llena, ya que un número pequeño de electrones posee suficiente energía térmica como para pasar a la otra banda. En esta banda los electrones son cuasi-libres y responden fácilmente al aplicar un campo E, y constituir una corriente. Por lo tanto a esta banda se la llama de conducción (BC). La tasa de generación térmica de portadores se denota  $G_{th}(T)$ . La tasa de generación por efecto óptico se nota  $G_{op}$  y es esencialmente independiente de la temperatura. Entonces:

$$G = G_{th}(T) + G_{op} \tag{1.2}$$

Por otro lado, cuando un electrón de la banda de conducción y un hueco de la banda de valencia se encuentran, se recombinan recomponiendo el enlace covalente. Este mecanismo, compensa y balancea la producción de portadores. Puede clasificarse de acuerdo al tipo de energía liberada.

- Recombinación térmica: la recombinación se traduce en calor. Este es el tipo predominante en silicio.

- Recombinación óptica: la recombinación produce un fotón. Este mecanismo es la base del funcionamiento de los LEDs. Casi inexistente en el Si, pero muy significativo en el GaAs.

Equilibrio térmico: está definido por la inexistencia de intercambio de energía del sistema con el medio exterior. En términos prácticos, esto se da ante la ausencia prolongada de estímulos externos (excitación óptica o campos eléctricos aplicados), a una temperatura constante. En este caso especial

se define la concentración intrínseca de portadores en equilibrio térmico  $n_i$ :

$$n_i \triangleq n = p \tag{1.3}$$

Esta concentración satisface la Ley de Acción de Masas:

$$n_i^2 = \frac{G_{th}(T) + G_{op}}{k} \tag{1.4}$$

La cantidad de portadores excitados a la banda de conducción para una cierta temperatura T:

$$n_i = 2\left(\frac{2\pi\sqrt{m_n^* m_p^* kT}}{h^2}\right)^{\frac{3}{2}} e^{-\frac{E_g}{2kT}}$$

(1.5)

donde:

T = temperatura en grados Kelvin

k= Constante de Boltzman:  $1.38 \mathrm{x} 10^{-23} \mathrm{J/K}$  ó  $8.617 \mathrm{x} 10^{-5} \mathrm{eV/K}$

h =Constante de Planck:  $6.626 \text{x} 10^{-34} \text{ J} \cdot \text{s}$

$E_g = \mathbf{energia} \ \mathbf{de} \ \mathbf{gap}$

$m_n^* =$ masa efectiva de electrones  $m_p^* =$ masa efectiva de huecos

#### 1.3. Semiconductores extrínsecos

Para modificar la conducción, se contamina o dopa el silicio con átomos de otros elementos denominados *impurezas*.

| Tipo N                         | Tipo P                      |

|--------------------------------|-----------------------------|

| Donores $N_D$                  | Aceptores $N_A$             |

| Mayoritarios: electrones       | Mayoritarios: huecos        |

| Dopado con átomos de un        | Dopado con átomos de un     |

| grupo mayor (grupo V)          | grupo menor (grupo III)     |

| Aumenta cantidad de electrones | Aumenta el numero de huecos |

| en la banda de conducción      | en la banda de valencia     |

Concentración de portadores mayoritarios:

$$n_0 = \frac{(N_D - N_A)}{2} + \sqrt{\frac{(N_D - N_A)^2}{4} + n_i^2}$$

(1.6)

Si los portadores mayoritarios son huecos, la ecuación 1.6 cambia  $n_0$  por  $p_0$  y se intercambian  $N_D$  con  $N_A$ .

Además, se cumple que:

$$p_0 = \frac{n_i^2}{n_0} \tag{1.7}$$

De la ecuación 1.7 se puede obtener la concentración de portadores minoritarios. En general, la concentración de dopantes es mucho mayor que la concentración intrínseca de portadores  $n_i$ , por lo que se puede considerar que la concentración de portadores mayoritarios es muy similar a la concentración de dopantes. El dopado produce un corrimiento en el nivel de Fermi  $E_f$ . En el caso del tipo N lo hace hacia la banda de conducción y se coloca encima del nivel  $E_d$ . En cambio, para el dopado tipo P, el corrimiento se produce hacia la banda de valencia, colocándose debajo del nivel  $E_a$

#### 1.4. Mecanismos de conducción

El primer mecanismo ocurre cuando un campo eléctrico aplicado produce una fuerza de arrastre sobre los portadores, forzando el movimiento. El segundo mecanismo ocurre cuando la concentración de portadores es mayor en un lugar que en otro, de manera que los portadores (movilizados, aleatoriamente, por acción de la temperatura) difunden de la zona de mayor concentración a la de menor concentración. En la mayoría de los casos, es posible representar el movimiento de portadores por uno solo de estos mecanismos.

#### 1.4.1. Movilidad de portadores

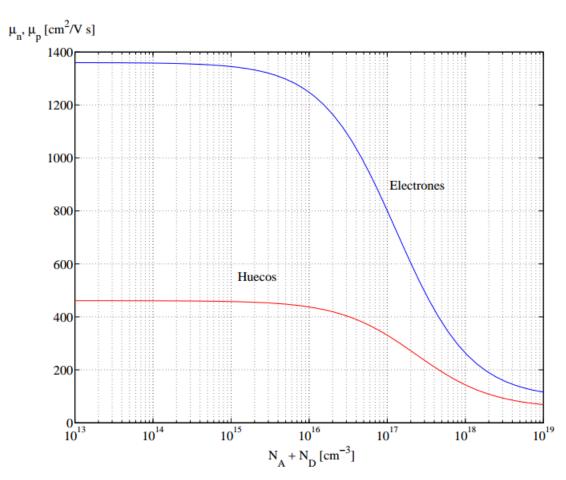

Las movilidades de huecos y electrones no son constantes, sino que varían de acuerdo al dopaje del semiconductor. Cuanto mayor sea la concentración del impurezas en el material, mayor será la probabilidad de que un electrón o hueco interactúe con la red cristalina produciendo colisiones.

Figura 1.3: Movilidad de huecos y electrones en silicio en función del dopado neto

Otro efecto en la conducción sucede con el aumento de la temperatura, el cual produce mayores efectos de colisión, reduciendo la movilidad. La movilidad de portadores en silicio puede aproximarse por la siguiente fórmula empírica, cuyo gráfico se muestra en la figura 1.3:

$$\mu = \mu_{min} + \frac{\mu_0}{1 + (N/N_{ref})^{\alpha}} \tag{1.8}$$

Donde:

|             | electrones                             | huecos                                  |

|-------------|----------------------------------------|-----------------------------------------|

| $N_{ref}$   | $1.3 \text{x} 10^{17} \text{ cm}^{-3}$ | $2.35 \text{x} 10^{17} \text{ cm}^{-3}$ |

| $\mu_{min}$ | $92 \text{ cm}^2/\text{Vs}$            | $54.3~\mathrm{cm^2/Vs}$                 |

| $\mu_0$     | $1268 \mathrm{~cm^2/Vs}$               | $406.9 \text{ cm}^2/\text{Vs}$          |

| $\alpha$    | 0.91                                   | 0.88                                    |

Pueden modelarse los efectos de de la temperatura de cada uno de estos parámetros de acuerdo a la siguiente fórmula:

$$[parametro] = [parametro]_{300K} \left(\frac{T_K}{300}\right)^{\eta}$$

(1.9)

Donde  $\eta$  depende del parámetro. Para el caso del silicio:

|         | $N_{ref}$ | $\mu_{min}$ | $\mu_0 \; (e^-)$ | $\mu_0~(\mathrm{h^+})$ | α      |

|---------|-----------|-------------|------------------|------------------------|--------|

| $\eta:$ | 2.4       | -0.57       | -2.33            | -2.23                  | -0.146 |

Por último, conforme el campo eléctrico aumenta, la velocidad de los portadores comienza a experimentar un efecto de saturación.

#### 1.4.2. Densidad de corriente de arrastre

La corriente de arrastre tiene la misma dirección que el campo eléctrico aplicado. Ésta se calcula como:

$$J_p{}^a = p_0 q \mu_p \overrightarrow{E} \qquad (huecos) \tag{1.10}$$

$$J_n^{\ a} = n_0 q \mu_n \overrightarrow{E} \qquad (electrones) \tag{1.11}$$

Tienen unidades de Ampére/ud de área (p.e A/cm).

Y la densidad de corriente de arrastre total es la suma de ambas:

$$J^a = J_p{}^a + J_n{}^a = \sigma \overrightarrow{E} \tag{1.12}$$

Donde la  $conductividad \sigma$  es:

$$\sigma = q(n_0\mu_n + p_0\mu_n) \tag{1.13}$$

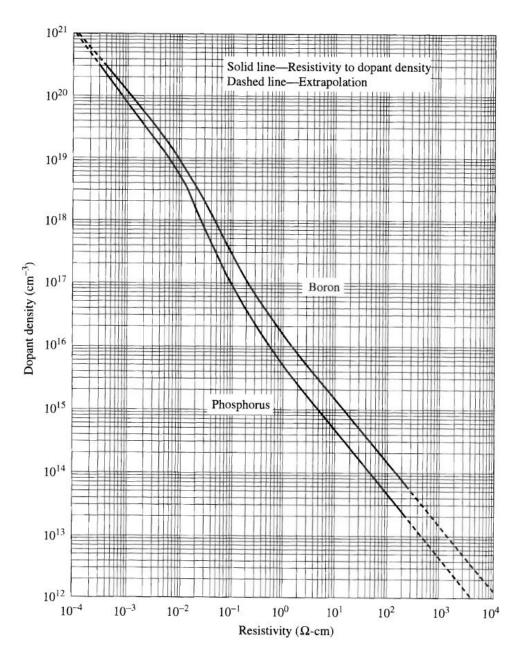

La figura 1.4 muestra un gráfico de la resistividad (inversa de la conductividad) en función de la densidad de dopantes para una temperatura de 23°C, de silicio dopado con Boro (grupo III) y Fósforo (grupo V).

Figura 1.4: Resistividad en función de la densidad de dopantes.

Nótese que la corriente es proporcional al producto del número de portadores y la movilidad. El aumento de dopado hace que el número de portadores aumente y que la movilidad disminuya. Debido a los órdenes de magnitud en los que varían estos dos términos, el efecto neto del dopado es el aumento de la conducción de corriente, debido al aumento de la cantidad de portadores.

Por otro lado, la corriente se calcula como la densidad de corriente por unidad de área:

$$i = J \cdot A \tag{1.14}$$

Además, la velocidad de arrastre (que está relacionada con la densidad de corriente de arrastre) se calcula como:

$$v_p{}^a = -\mu_p \overrightarrow{E} \qquad (huecos) \tag{1.15}$$

$$v_n^a = -\mu_n \overrightarrow{E}$$

(electrones) (1.16)

Tiene signo negativo porque va en dirección contraria que el campo eléctrico.

#### 1.4.3. Densidad de corriente de difusión

La densidad de corriente de difusión de huecos y electrones se calcula, respectivamente como:

$$J_p^{\ d} = -qD_p \frac{dp(x)}{dx} \tag{1.17}$$

$$J_n^{\ d} = qD_n \frac{dn(x)}{dx} \tag{1.18}$$

Donde  $D_p$  y  $D_n$  es el coeficiente de difusividad de huecos y electrones, que se calcula como:

$$D_{p/n} = \frac{\lambda^2}{2\tau_c} \tag{1.19}$$

La **tensión térmica**<sup>1</sup> se define como:

$$V_{th} \triangleq \frac{kT}{q} \tag{1.20}$$

Y posee un valor de 25.9 mV a temperatura ambiente.

Además, el coeficiente de difusividad puede definirse mediante la relación de Einstein:

$$D_{n/n} = \mu_{n/n} \cdot V_{th} \tag{1.21}$$

La relación entre el voltaje aplicado a un semiconductor de longitud L y el campo eléctrico que circula por él es:

$$\Delta V = \int_0^L E(x)dx \tag{1.22}$$

En general el campo eléctrico es constante, entonces queda:

$$\Delta V = E \cdot L \qquad [V] \tag{1.23}$$

<sup>&</sup>lt;sup>1</sup>En algunas bibliografías se denota  $U_T$ .

#### 2. Electrostática de los semiconductores

Considerando un semiconductor no uniformemente dopado, con una densidad de dopantes  $N_d(x)$ , la difusión de portadores debe equilibrar al arrastre en todo punto<sup>2</sup>:

$$J_n(x) = J_n^{\ a}(x) + J_n^{\ d}(x) = 0 \tag{2.1}$$

Como la densidad de dopantes no es igual a la densidad de portadores, en general, se producen ciertos efectos:

#### 2.1. Densidad de carga espacial $\rho$

$$\rho(x) = q[N_d(x) - n_0(x)] \tag{2.2}$$

#### 2.2. Campo eléctrico E

$$E(x) - E(0) = \frac{1}{\epsilon_s} \int_0^x \rho(x) dx \tag{2.3}$$

#### 2.3. Potencial electrostático o de built-in $\phi$

$$\phi(x) - \phi(0) = -\int_0^x E(x)dx$$

(2.4)

#### 2.3.1. Regla de los 60 mV

Esta regla permite calcular fácilmente, el potencial de una especie de silicio dopado respecto a silicio intrínseco: por cada orden de magnitud de dopado con respecto a silicio intrínseco, se producen 60mV adicionales de tensión:

$$\phi(x) = 60mV \cdot log\left(\frac{n_b}{10^{10}}\right) \qquad (electrones)$$

(2.5)

$$\phi(x) = -60mV \cdot log\left(\frac{p_b}{10^{10}}\right) \qquad (huecos)$$

(2.6)

#### 2.4. Aproximación de cuasi-neutralidad

Establece que como  $n_0(x)$  sigue bien a  $N_d(x)$ , la carga espacial es mínima y el semiconductor es cuasi-neutral. La hipótesis de cuasi-neutralidad es válida si:

$$\left|\frac{n_0 - N_d}{n_0}\right| \ll 1$$

$o \qquad \left|\frac{n_0 - N_d}{N_d}\right| \ll 1$  (2.7)

#### 2.5. Relación de Boltzman

Los electrones de un SC en equilibrio térmico cumplen con 2.1. Utilizando las relaciones de Einstein y considerando que  $\phi_{ref} = 0$  cuando  $n_0(ref) = n_i$ , se obtiene la relación de Boltzman:

$$n_0 = n_i \cdot e^{\phi/V_{th}} \tag{2.8}$$

$<sup>^2</sup>$ Las ecuaciones están para los electrones, pero valen también para los huecos.

Para huecos:

$$n_0 = n_i \cdot e^{-\phi/V_{th}} \tag{2.9}$$

Y se pueden reescribir como:

$$\phi_n = V_{th} \cdot \ln \frac{n_0}{n_i}$$

(electrones) (2.10)

$$\phi_p = -V_{th} \cdot \ln \frac{p_0}{n_i} \qquad (huecos) \tag{2.11}$$

# 3. Juntura PN

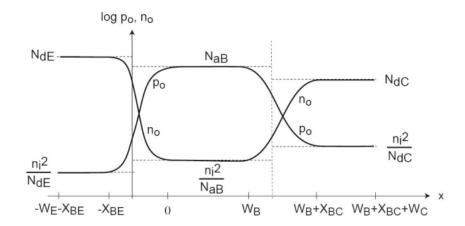

Al poner en contacto una pieza se silicio dopada tipo N con otra dopada tipo P, puede observarse la siguiente distribución de portadores:

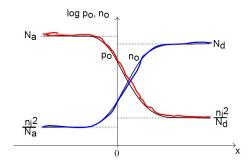

Figura 3.1: Distribución de portadores en la juntura PN

Lejos de la juntura PN (el x=0 en la figura 3.1) no pasa nada. Éstas se denominan regiones cuasi-neutrales (P-QNR a la izquierda y N-QNR a la derecha).

Cerca de la juntura, la corriente de arrastre debe cancelar a la corriente de difusión. Esta es la denominada región de carga espacial (SCR).

Para determinar  $n_0(x), p_0(x), \rho(x), E(x)$  y  $\phi(x)$ , se utiliza la aproximación de vaciamiento.

# 3.1. Aproximación de vaciamiento

Esta aproximación consiste en suponer que en la región de vaciamiento no hay portadores -ni mayoritarios, ni minoritarios. En resumen:

- Las QNRs tienen neutralidad de carga.

- La SCR está <u>vacía</u> de portadores.

- La transición entre las QNRs y la SCR es <u>abrupta</u> (hay que calcular  $x_{n_0}$  y  $-x_{p_0}$ ).

Figura 3.2: Aproximación de vaciamiento

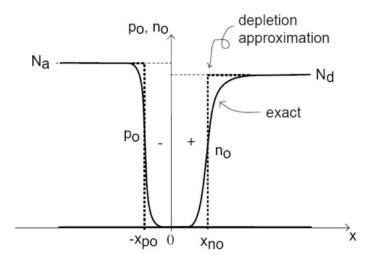

Con esta aproximación, la densidad de carga espacial en la SCR queda:

Zona tipo

$$P \rho = -q N_a$$

Zona tipo  $N \rho = q N_d$  (3.1)

El campo eléctrico:

Zona tipo P

$$E(x) = -\frac{qN_a}{\epsilon_{Si}}(x + x_{p_0})$$

Zona tipo N  $E(x) = \frac{qN_d}{\epsilon_{Si}}(x - x_{n_0})$  (3.2)

La continuidad del campo eléctrico (dado que no hay cambio de material) implica que las expresiones halladas para las regiones de vaciamiento P y N, deben ser iguales en x = 0, donde surge que:

$$N_a x_{p_0} = N_d x_{p_0} (3.3)$$

Se deduce que la zona de vaciamiento tiene menor profundidad de penetración en el lado de mayor concentración de impurezas. Esto es equivalente a decir que la zona de vaciamiento se desarrolla, mayormente, en la región de menor dopado.

Integrando el campo eléctrico, se obtiene el **potencial**<sup>3</sup>:

$$P - QNR \phi_p = -V_{th} \ln \frac{N_a}{n_i}$$

$$N - QNR \phi_n = V_{th} \ln \frac{N_d}{n_i}$$

(3.4)

Definiendo así el **potencial de juntura**:

$$\phi_B = \phi_n - \phi_p = V_{th} \ln \frac{N_a N_d}{n_i^2} \tag{3.5}$$

En la región de vaciamiento:

$$SCR tipo P \phi(x) = \phi_p + \frac{1}{2} \frac{qN_a}{\epsilon_{Si}} (x + x_{p_0})^2$$

$$SCR tipo N \phi(x) = \phi_n - \frac{1}{2} \frac{qN_d}{\epsilon_{Si}} (x - x_{n_0})^2$$

(3.6)

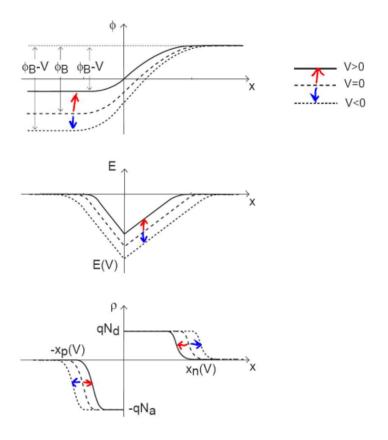

La figura 3.3 ilustra estas últimas ecuaciones:

<sup>&</sup>lt;sup>3</sup>Definiendo  $\phi = 0$  @  $n_0 = p_0 = n_i$

Figura 3.3: Gráficos de densidad de carga espacial, campo eléctrico y potencial electrostático para una juntura PN

Luego, pidiendo dos condiciones:

- Neutralidad global de carga eléctrica.

- $\phi(x)$  continua en x=0

Se obtienen los límites de la región de vaciamiento,  $x_{n_0}$  y  $x_{p_0}$ :

$$x_{n_0} = \sqrt{\frac{2\epsilon_{Si}\phi_B N_a}{q(N_a + N_d)N_d}}$$

$$x_{p_0} = \sqrt{\frac{2\epsilon_{Si}\phi_B N_d}{q(N_a + N_d)N_a}}$$

(3.7)

También se obtiene el campo eléctrico en la juntura:

$$|E_0| = \sqrt{\frac{2q\phi_B N_a N_d}{\epsilon_{Si}(N_a + N_d)}} \tag{3.8}$$

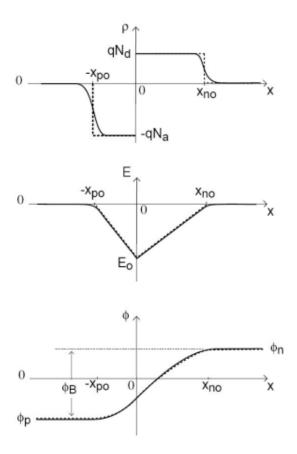

#### 3.1.1. Casos de interés

- $\bullet\,$  Juntura simétrica:  $N_a=N_d\Rightarrow x_{p_0}=x_{n_0}$

- Juntura asimétrica:  $N_a > N_d \Rightarrow x_{p_0} < x_{n_0}$  ó  $N_a < N_d \Rightarrow x_{p_0} > x_{n_0}$

#### • Juntura muy asimétrica:

$$\circ \ \mathbf{p}^{+}\mathbf{n} \colon N_{a} \gg N_{d} \Rightarrow x_{p_{0}} \ll x_{n_{0}}$$

$$\circ$$

n<sup>+</sup>p:  $N_a \ll N_d \Rightarrow x_{p_0} \gg x_{n_0}$

El lado poco dopado controla la electrostática de la juntura:

Figura 3.4: Junturas de interés.

# 3.2. Electrostática de la juntura PN con polarización aplicada

Convención de signos:

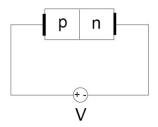

Figura 3.5:

V > 0 polarización directa, forward bias V < 0 polarización inversa, reverse bias

La batería impone una diferencia de potencial a lo largo de la juntura. El potencial V cae en la zona desierta. La electrostática se modifica como se muestra en la figura 3.6.

En directa la diferencia de potencial de la zona desierta disminuye  $\Rightarrow |E|$  disminuye  $\Rightarrow x_d^4$  disminuye. En inversa la diferencia de potencial de la zona desierta aumenta  $\Rightarrow |E|$  aumenta  $\Rightarrow x_d$  aumenta.

Esencialmente, la electrostática de la juntura PN no se modifica cualitativamente respecto del equilibrio térmico. Solo se modifica el dipolo de carga en la zona desierta de modo de compensar el potencial forzado externamente.

$<sup>^4</sup>x_d = x_{n_0} + x_{p_0}$

Figura 3.6: Electrostática de la juntura con polarización.

La formulación analítica de la electrostática de la juntura PN polarizada es idéntica a la del equilibrio térmico, pero considerando:  $\phi_B \to \phi_B - V$

Los parámetros  $x_{n_0},\,x_{p_0},\,x_d$ y  $|E_0|$  pueden escribirse como:

$$[parametro]_V = [parametro]_0 \sqrt{1 - \frac{V}{\phi_B}}$$

(3.9)

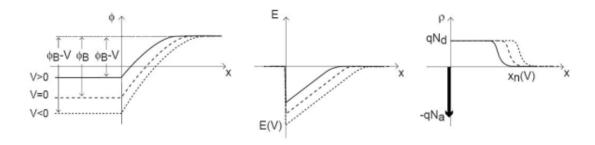

En una juntura fuertemente asimétrica, todos los cambios tienen lugar en el lado menos dopado:

Figura 3.7: Electrostática en juntura muy asimétrica. Electrostática en juntura muy asimétrica.

## 3.3. Capacidad de juntura

La capacidad de juntura es producto de la carga neta acumulada en la zona de vaciamiento. Al aplicar un pequeño incremento de tensión, esta carga acumulada presenta una variación en los extremos de la zona desierta (negativa para el lado tipo P y positiva para el lado tipo N). Si consideramos solamente la variación de carga, vemos que está separada por una distancia  $x_d$  y son opuestas, por lo que se puede considerar como un capacitor de placas planas paralelas con capacidad  $C_j$ .

Esta capacidad se calcula como:

$$C'_{j}(V) = \sqrt{\frac{q\epsilon_{Si}N_{a}N_{d}}{2(\phi_{B} - V)(N_{a} + N_{d})}}$$

$$= C'_{j0}\frac{1}{\sqrt{1 - \frac{V}{\phi_{B}}}}$$

(3.10)

Donde  $C'_{j0}$  es la capacidad de juntura sin polarización aplicada (V = 0). Esta capacidad se expresa como carga por unidad de área. La capacidad se calcula como:

$$C_j(V) = C_j' \cdot A \tag{3.11}$$

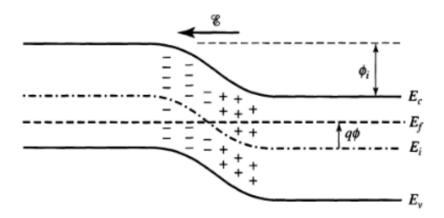

## 3.4. Diagrama de bandas de energía

En el caso de la juntura sin tensión externa aplicada, es decir en equilibrio térmico se tiene el siguiente diagrama de bandas:

Figura 3.8: Diagrama de bandas de energía para una juntura PN en equilibrio térmico.

Donde:

$$\phi_i = E_0 - E_c$$

$$q\phi_0 = E_f - E_i$$

$$\phi_0 = \phi_B$$

(3.12)

#### 4. Diodo PN

En equilibrio térmico, hay un balance dinámico entre difusión y arrastre de electrones y huecos:

$$|J_{arr}| = |J_{dif}| \tag{4.1}$$

Al aplicar una tensión de polarización, la concentración de portadores se modifica y en consecuencia se altera el balance de corrientes.

• Si

$$V > 0 \Rightarrow |E_{SCR}| \downarrow \Rightarrow |J_{arr}| \downarrow$$

$$|J_{arr}| < |J_{dif}| \qquad (4.2)$$

Debido a este desbalance, aparece una corriente eléctrica neta (de difusi'on)  $\Rightarrow$  se inyectan huecos en la n-QNR y electrones en la p-QNR, produciendo un exceso de minoritarios en las regiones cuasi-neutrales.

Como hay una gran difusión de  $h^+$  en n-QNR y de  $e^-$  en p-QNR  $\Rightarrow$  la corriente puede ser grande.

• Si

$$V < 0 \Rightarrow |E_{SCR}| \uparrow \Rightarrow |J_{arr}| \uparrow$$

$$|J_{arr}| > |J_{dif}| \tag{4.3}$$

Debido a este desbalance, aparece una corriente eléctrica neta (de arrastre)  $\Rightarrow$  se extraen huecos de la n-QNR y electrones de la p-QNR, produciendo un déficit de minoritarios en las regiones cuasi-neutrales.

Como hace falta compensar pocos  $h^+$  en n-QNR y  $e^-$  en p-QNR  $\Rightarrow$  la corriente es pequeña.

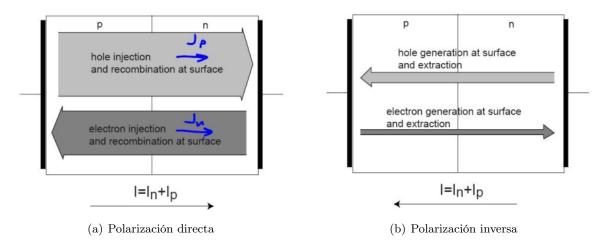

En **polarización directa**, los minoritarios inyectados se difunden a través de la región QNR y se recombinan en la superficie del semiconductor (fig. 4.1(a)).

En **polarización inversa**, los minoritarios son arrastrados por campo eléctrico en la zona desierta. Se generan en la superficie y se difunden a través de las regiones cuasi-neutrales (fig. 4.1(b)).

Figura 4.1: Corrientes en polarización de juntura PN

El factor limitante de la corriente del diodo es el gradiente de difusión en las regiones cuasi-neutrales. Este modelo es válido mientras se cumpla que el nivel de exceso de portadores minoritarios en los bordes de la zona desierta sea mucho menor que la concentración de mayoritarios, es decir:

$$n(-x_p) \ll N_a \qquad y \qquad p(x_n) \ll N_d$$

(4.4)

Esto se conoce como la hipótesis de bajo nivel de inyección.

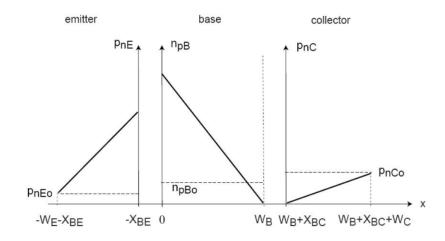

## 4.1. Corrientes de difusión en las QNR

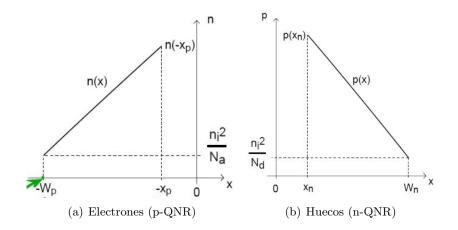

En las regiones cuasi-neutrales, los portadores minoritarios se difunden sin recombinarse hasta alcanzar el contacto, por lo tanto los perfiles de distribución de portadores debe ser lineal (p(x) y n(x)). En los extremos (W), la concentración debe ser  $n_i^2/N$  (N concentración de dopantes).

El perfil de concentración de portadores minoritarios en las QNRs resulta:

Figura 4.2: Perfiles de concentración de portadores minoritarios en las QNRs.

De donde se obtienen las densidades de corrientes:

$$J_n = q \frac{n_i^2}{N_a} \frac{D_n}{W_p - x_p} \left( \exp \frac{qV}{kT} - 1 \right)$$

$$J_p = q \frac{n_i^2}{N_d} \frac{D_p}{W_n - x_n} \left( \exp \frac{qV}{kT} - 1 \right)$$

$$(4.5)$$

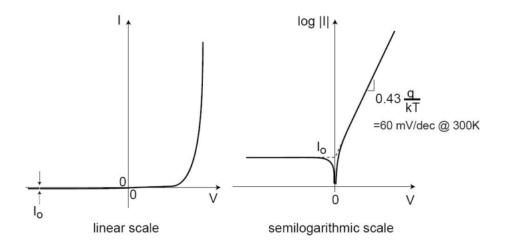

Luego, sumando ambos componentes y multiplicando por el área, se obtiene la corriente total (ecuación característica I-V):

$$I = I_0 \left( \exp \frac{qV}{kT} - 1 \right) \tag{4.6}$$

Donde  $I_0$  es la corriente de saturación:

$$I_0 = qAn_i^2 \left( \frac{1}{N_a} \frac{D_n}{W_n - x_p} + \frac{1}{N_d} \frac{D_p}{W_n - x_n} \right)$$

(4.7)

La temperatura afecta las características del diodo, provocando un aumento de corriente con la temperatura.

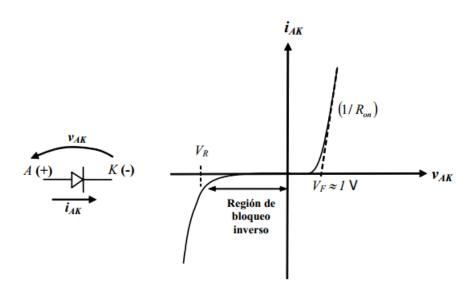

Figura 4.3: Curva característica I-V del diodo PN

#### 4.2. Resolver ejercicios de polarización de diodo

- 1. Suponer un régimen (directa o inversa).

- 2. Determinar el valor de la corriente.

- 3. Verificar que el régimen propuesto es el correcto. De lo contrario volver al punto 1.

#### 4.3. Modelo de orden 0

Es una aproximación utilizada para resolver más fácilmente los problemas de polarización de diodos. En este modelo se considera:

• Directa:

$$\begin{cases} V_D = V_{D_{ON}} \\ I_D > 0 \end{cases}$$

• Inversa:

$$\begin{cases} V_D \neq V_{D_{ON}} \\ I_D \approx -I_0 \approx 0 \end{cases}$$

# 4.4. Modelo de pequeña señal

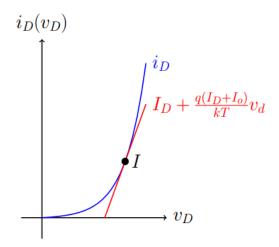

La tensión total aplicada sobre el diodo  $v_D(t)$ , en general es la superposición de una tensión continua  $V_D$  y una pequeña señal dependiente del tiempo  $v_d(t)$ :

$$v_D(t) = V_D + v_d(t) \tag{4.8}$$

Si  $v_d(t)$  es lo suficientemente pequeña, es posible linealizar la exponencial de la corriente  $i_D(t)$  en un entorno del punto de reposo, mediante el desarrollo de Taylor, tomando los términos de orden cero y uno. De esto se deduce que la corriente de pequeña señal es:

$$i_d(t) = \frac{I_D + I_0}{\frac{kT}{a}} \cdot v_d(t) \tag{4.9}$$

De esta forma, estamos aproximando la curva característica del diodo con una recta. Ambas coinciden en el *punto de polarización*, también llamado punto de trabajo o de reposo:

Figura 4.4: Aproximación  $i_D(v_D)$

Este modelo es válido mientras que:

$$|v_d| < 10mV(pico) \tag{4.10}$$

#### 4.4.1. Parámetros de pequeña señal

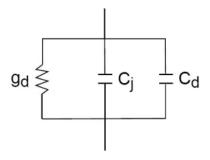

Figura 4.5: Modelo de pequeña señal de un diodo

#### Conductancia:

$$g_d = \frac{\partial i_D}{\partial v_D}\Big|_{(I_D, V_D)} = \frac{I_D + I_0}{\frac{kT}{a}} \tag{4.11}$$

Capacidad de juntura: es la misma que la estudiada en la juntura PN.

$$C'_{j}(V) = \sqrt{\frac{q\epsilon_{Si}N_{a}N_{d}}{2(\phi_{B} - V)(N_{a} + N_{d})}}$$

$$= C'_{j0} \frac{1}{\sqrt{1 - \frac{V}{\phi_{B}}}}$$

(4.12)

Donde  $C'_{j0}$  es la capacidad de juntura sin polarización aplicada (V = 0). Esta capacidad se expresa como carga por unidad de área. La capacidad se calcula como:

$$C_j(V) = \frac{\partial q_{SCR}}{\partial v_D}\Big|_{(I_D, V_D)} = C'_j \cdot A \tag{4.13}$$

En directa, para tensiones mayores a  $\phi_B/2$  la capacidad de juntura suele tomarse como constante (o despreciarse) con el siguiente valor:

$$C_j = \sqrt{2}C_{j0} \tag{4.14}$$

Es esta la capacidad predominante al polarizar el diodo en inversa.

#### Capacidad de difusión:

La aplicación de un potencial en directa causa la circulación de una corriente directa de difusión. En esta situación se forman perfiles de carga en la zona P y en la zona N, que son los causantes de la corriente de difusión. Esta carga acumulada varía, de acuerdo al potencial aplicado y, por ende, esta variación incremental de carga puede ser interpretada como una capacidad incremental. De hecho, si se quiere reducir la circulación de corriente por el diodo a cero, primero debe eliminarse esta carga, tal como si se tratase de un capacitor.

$$C_d = \frac{\partial q_{QNR}}{\partial v_D}\Big|_{(I_D, V_D)} = \frac{\tau_T}{V_{th}} (I_D + I_0) \begin{cases} C_{dn} = \frac{\tau_p}{V_{th}} I_p \\ C_{dp} = \frac{\tau_n}{V_{th}} I_n \end{cases}$$

(4.15)

Donde El **tiempo de tránsito de huecos** es *el tiempo medio empleado por un hueco para difundirse* a través de la región n-QNR:

$$\tau_{T_p} = \frac{(W_n - x_n)^2}{2D_p} \tag{4.16}$$

Y el tiempo de tránsito de electrones a través de la región p-QNR:

$$\tau_{T_n} = \frac{(W_p - x_p)^2}{2D_n} \tag{4.17}$$

Y el tiempo de tránsito total:

$$\tau_T = \frac{(qA(W_p n_p + W_n p_n))}{2I_0} \tag{4.18}$$

La capacidad total en directa es la suma de la capacidad de juntura y la de difusión, pero como se puede apreciar los valores resultantes, la capacidad de difusión domina la capacidad directa.

#### 4.5. El diodo real

#### 4.5.1. Coeficiente de emisión

Al coeficiente de emisión o factor de idealidad se lo identifica con la letra n y modifica la expresión de la corriente del diodo de la siguiente forma:

$$i_D = I_0 \left[ \exp \frac{v_D}{n \frac{kT}{a}} - 1 \right] \tag{4.19}$$

Dependiendo del diodo, el tipo de SC y el proceso de fabricación, n puede tomar valores entre 1 y 2.

El factor empírico n debe introducirse ya que ciertas hipótesis asumidas al momento de plantear el modelo para hallar la transferencia del diodo en la práctica no se cumplen con de forma rigurosa. Por ejemplo:

- En la hipótesis de *diodo corto* se asume que **no existe recombinación de portadores en el** cuerpo del diodo.

- En la hipótesis de vaciamiento se asume una juntura metalúrgica perfecta.

#### 4.5.2. Corriente de generación en la zona desierta

En un diodo real existe una generación neta de portadores en la zona desierta. La recombinación es muy baja, por lo tanto prevalece la generación. Estos pares generados térmicamente son separados por el campo eléctrico presente en la juntura y arrastrados en direcciones opuestas. La corriente generada en la zona desierta tiene la siguiente expresión:

$$I_{0_{(gen)}} = \frac{qAn_i x_d(V)}{\tau_q} \tag{4.20}$$

Donde  $x_d(V)$  es el ancho de la zona desierta y  $\tau_q$  es el tiempo medio de generación.

Para considerar esta corriente de generación usualmente se modifica el modelo del diodo de la siguiente forma:

$$I_{0_{(real)}} = I_{0_{(ideal)}} + I_{0_{(gen)}}$$

(4.21)

#### 4.5.3. Resistencia serie

El SC presenta una resistividad que depende del nivel de dopaje. Para corrientes bajas este efecto puede despreciarse, pero al incrementarse la corriente la caída de potencial que ocurre en el cuerpo del SC hace que la tensión aplicada en los terminales del diodo difiera de la aplicada en la juntura.

Los contactos metal-semiconductor también presentan un efecto resistivo adicional.

Ambos fenómenos suelen moderarse considerando una resistencia conectada en serie con el diodo.

El efecto observado es que la corriente del diodo es menor a la del modelo ideal al aumentar la tensión aplicada.

#### 4.6. Ruptura inversa

Al polarizar un diodo en inversa, aumenta la diferencia de potencial en la juntura respecto del equilibrio, aumentando el campo eléctrico interno.

Los campos eléctricos elevados en la juntura pueden producir la ruptura inversa de la juntura. Se llama ruptura inversa al incremento abrupto del módulo de la corriente para una tensión inversa determinada. Dependiendo del circuito externo, este efecto puede o no destruir el dispositivo.

Existen dos fenómenos físicos asociados con la ruptura inversa de la juntura:

- Efecto avalancha: ocurre en junturas levemente dopadas.

- Efecto túnel: ocurre en junturas fuertemente dopadas.

El diodo zener es un ejemplo de aplicación de la ruptura inversa.

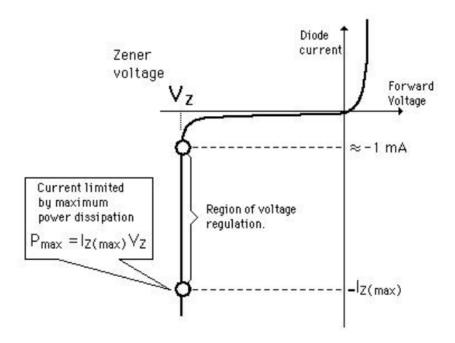

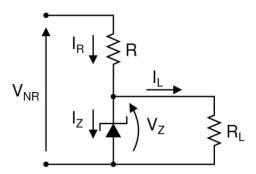

#### 4.7. Diodo Zener

Debido a que en polarización inversa el diodo Zener presenta una región de tensión casi constante para un rango amplio de corrientes, se los utiliza para obtener una tensión regulada.

Figura 4.6: Curva característica del diodo Zener

Figura 4.7: Circuito típico con diodo Zener

Para elegir la resistencia limitadora R adecuada hay que calcular cuál puede ser su valor mínimo y máximo de acuerdo con la corriente  $I_L$  máxima y mínima, las corrientes de Zener máximas y mínimas y las tensiones  $V_{NR}$  máximas y mínimas:

$$\begin{cases}

R_{min} = \frac{V_{NR,max} - V_Z}{I_{L,min} + I_{Z,max}} \\

R_{max} = \frac{V_{NR,min} - V_Z}{I_{L,max} + I_{Z,min}}

\end{cases}$$

(4.22)

#### 5. Juntura MOS

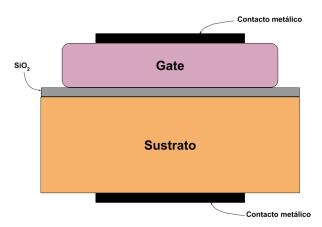

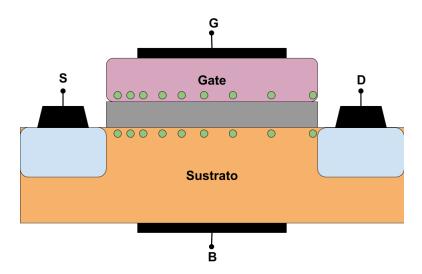

Un capacitor MOS está compuesto por una compuerta o gate, un dieléctrico y un sustrato o bulk:

Figura 5.1: Estructura MOS

En la actualidad, el gate se fabrica utilizando silicio policristalino (silicio cristalino por dominios o regiones), también conocido como polisilicio. Para disminuir la resistencia del gate, es habitual doparlo fuertemente. El dieléctrico es una lámina extremadamente delgada de dióxido de silicio, que se logra oxidando el silicio mediante la exposición del mismo a una atmósfera con oxígeno, a una cierta temperatura. El sustrato es la oblea o wafer de silicio que se halla, por lo general, levemente dopada.

Dado que el dispositivo es un capacitor, en estado estacionario, no habrá circulación de corriente continua, y el dispositivo se hallará en equilibrio térmico aún en presencia de potenciales externos aplicados.

Debido a que los dopajes son "desiguales" (el *gate* tiene un dopaje más fuerte que el sustrato) pueden darse 4 combinaciones<sup>5</sup>:

| Gate            | Bulk | $\phi_{gate}$     | $\phi_{bulk}$              | $\phi_B$                  | $V_{FB} = -\phi_B$ | $V_T$              |

|-----------------|------|-------------------|----------------------------|---------------------------|--------------------|--------------------|

| N++             | P    | $550 \mathrm{mV}$ | $-550mV < \phi_{bulk} < 0$ | $550mV < \phi_B < 1.1V$   | < 0                | $V_T > V_{FB}$     |

| $P^{++}$        | P    | -550 mV           | $-550mV < \phi_{bulk} < 0$ | $-550mV < \phi_B < 0V$    | > 0                | $V_T > V_{FB} > 0$ |

| N <sup>++</sup> | N    | $550 \mathrm{mV}$ | $0 < \phi_{bulk} < 550mV$  | $0 < \phi_B < 550 mV$     | < 0                | $V_T < V_{FB} < 0$ |

| P <sup>++</sup> | N    | -550mV            | $0 < \phi_{bulk} < 550mV$  | $-1.1V < \phi_B < -550mV$ | > 0                | $V_T < V_{FB}$     |

Cuadro 5.1: Potenciales para las diferentes combinaciones bulk-gate.

Es fácil notar que si el potencial de *flatband* (en valor absoluto), es menor que 550mV, entonces *gate* y el sustrato son del mismo tipo (ambos P o ambos N). Por el contrario, si está entre 1.1V y 550mV, entonces son de materiales contrarios (estas combinaciones son más comunes).

#### 5.1. Regimenes de la juntura MOS

Al aplicar una tensión entre gate y bulk, denominada  $v_{GB}$  las cargas en ellos se van modificando, generando diferentes efectos<sup>6</sup>.

Siempre se cumple que:

$$\phi_B + V_{GB} = \Delta V_{ox} + \Delta V_{bulk} \tag{5.1}$$

<sup>&</sup>lt;sup>5</sup>A partir de acá es necesario consultar la bibliografía y los vídeos para terminar de entender el resumen.

$<sup>^6</sup>$ Las ecuaciones que dependen de la polarización en las siguientes secciones corresponden a la combinación  $N^{++}P$

#### 5.1.1. Acumulación

En este modo de operación, se acumulan los portadores mayoritarios en el gate y en el sustrato, pegado al óxido. Aquí el dispositivo se comporta como un capacitor lineal ideal de placas paralelas.

En el modo de acumulación, la concentración de carga consiste en dos impulsos, de igual magnitud y signo contrario, a ambos lados del óxido.

El campo eléctrico es constante a lo largo del óxido, y la carga que se acumula se calcula como:

$$Q_G = \epsilon_{ox} v_{ox} \tag{5.2}$$

Y la capacidad del óxido por unidad de área<sup>7</sup>:

$$C'_{ox} \triangleq \frac{\epsilon_{ox}}{t_{ox}} \tag{5.3}$$

Donde  $t_{ox}$  es el espesor de la capa de óxido.

## 5.1.2. Potencial de banda plana (flatband)

Está caracterizado por la ausencia de cargas tanto en el gate como en el sustrato. Debido a esto, el campo eléctrico es nulo.

La tensión de *flatband* se define como:

$$V_{FB} \triangleq -\phi_B \tag{5.4}$$

#### 5.1.3. Vaciamiento

Se denomina así debido a la presencia de una zona de vaciamiento en el sustrato. En este modo de funcionamiento, el capacitor es no lineal, debido a la dependencia de la región de vaciamiento con el potencial aplicado.

Debido al alto dopado, la concentración de cargas se puede considerar como laminar, es decir, concentrada prácticamente por completo en la cara inferior del *gate* (en la interfaz con el óxido). En cambio, el sustrato si soporta carga en volumen.

La lámina de iones que aparece en el *gate* repele las cargas de signo contrario que aparecen debajo del óxido, produciendo una zona de vaciamiento.

El potencial total, desarrollado a lo largo del óxido es:

$$\Delta V_{ox} = \frac{Q_G}{C_{ox}'} \tag{5.5}$$

Con la carga  $Q_G$ :

$$Q_G = -Q_{bulk} = qN_{bulk}x_d (5.6)$$

Y el potencial desarrollado a lo largo de la zona de vaciamiento:

$$\Delta V_{bulk} = \frac{q N_{bulk}}{2\epsilon_{Si}} x_d^2 \tag{5.7}$$

Donde  $x_d$ , el ancho de la zona de vaciamiento, se calcula como:

$$x_d = \frac{\epsilon_{Si}}{C'_{ox}} \left( \sqrt{1 + \frac{4(\phi_B - V_{GB})}{\gamma^2}} - 1 \right)$$

(5.8)

<sup>&</sup>lt;sup>7</sup>Los parámetros  $C'_{ox}$ ,  $\phi_B$ ,  $\phi_{bulk}$  y  $\phi_{gate}$  no dependen de la polarización. En consecuencia, son independientes del régimen de operación.

Donde  $\gamma$  es el body factor coefficient (que se describirá en la sección de transistor MOSFET), se calcula como:

$$\gamma = \frac{1}{C_{ox}'} \sqrt{2\epsilon_{Si} q N_{bulk}} \tag{5.9}$$

#### 5.1.4. Tensión de umbral

La zona de vaciamiento máxima se alcanza para un valor de potencial de *gate* denominado "tensión de umbral".

$$\Delta V_{bulk} = -2\phi_p \tag{5.10}$$

$$\Delta V_{ox} = 2\phi_B + V_{GB} - \Delta V_{bulk} \tag{5.11}$$

#### 5.1.5. Inversión

Si se aumenta (o disminuye, dependiendo de la combinación gate-sustrato) la tensión  $V_{GB}$  por encima de  $V_T$ , se introduce más carga de portadores minoritarios en el gate, que debe ser balanceada por la carga debajo del óxido. Dado que la zona de vaciamiento no varía más, la única posibilidad para balancear la carga es que aparezcan portadores minoritarios debajo del óxido. En esta situación, se dice que el sustrato se ha invertido, dado que ahora posee portadores minoritarios. Estos portadores forman un canal.

La observación de los portadores en el canal haría pensar que el sustrato es de tipo contrario al dopaje con la misma concentración de impurezas (por ejemplo, uno pensaría que un sustrato tipo P es de tipo N, con un dopado  $N_d$  de la misma magnitud que  $N_a$ . Es por ello que esta condición se denomina inversión.

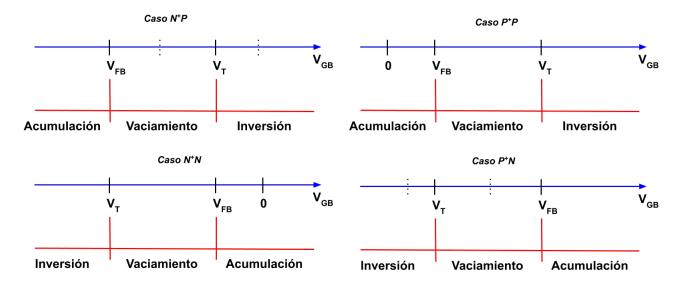

Figura 5.2: Regímenes de las diferentes combinaciones MOS para las diferentes tensiones de polarización aplicadas

Las líneas punteadas indican las posibles ubicaciones para  $V_{GB} = 0V$ .

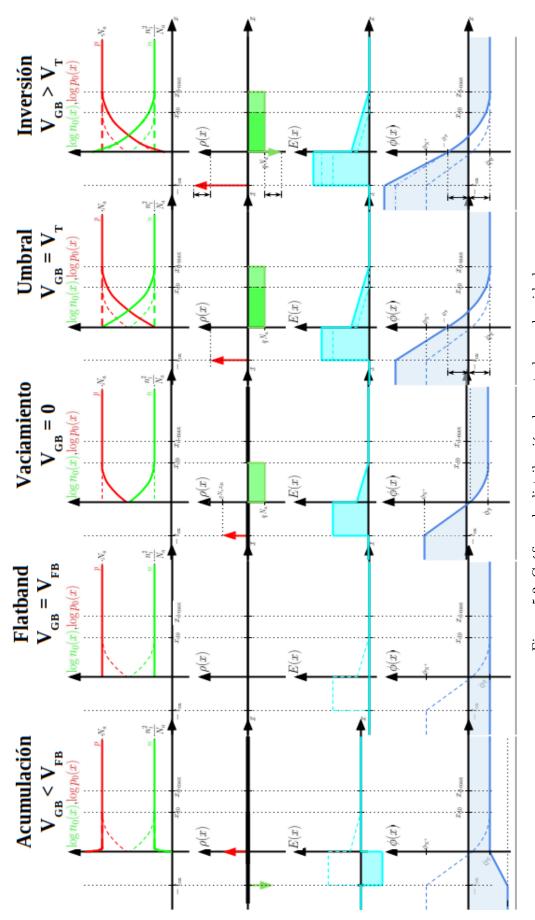

En la figura 5.3 se muestran los regímenes para una juntura MOS  $N^{++}P$ . Para la combinación  $P^{++}N$ , los gráficos se "espejan" verticalmente.

Figura 5.3: Gráficos de distribución de portadores, densidad de carga, campo eléctrico y potencial para una juntura MOS  $\rm N^{++}P.$

La expresión de la carga es no lineal con respecto a  $V_{GB}$  y puede resumirse, para cada una de las zonas de operación, de la siguiente forma:

$$Q_{G} = \begin{cases} C'_{ox}(V_{GB} - V_{FB}) & en \ acumulation \\ \frac{q\epsilon_{Si}N_{bulk}}{C'_{ox}} \left(-1 + \sqrt{1 + 2\frac{C'_{o}x^{2}(V_{GB} - V_{FB})}{q\epsilon_{Si}N_{bulk}}}\right) & en \ vaciamiento \\ C'_{ox}(V_{GB} - V_{FB} + \sqrt{2q\epsilon_{Si}N_{bulk}}(-2\phi_{p}) & en \ inversion \end{cases}$$

(5.12)

Para cada regimen de operación, dependiendo de la tensión  $V_{GB}$ , la capacidad incremental se puede hallar como:

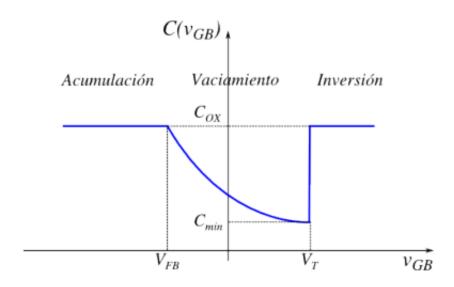

$$C = \left. \frac{dQ(v_{GB})}{dv_{GB}} \right|_{v_{GB}} \tag{5.13}$$

En acumulación el gate solamente aprecia la capacidad del óxido. En vaciamiento, la capacidad incremental es el producto de dos capacidades en serie: la del óxido y la de la zona de vaciamiento:

$$C_{vac} = \frac{\epsilon_{Si}}{x_d} \tag{5.14}$$

En inversión, la carga del sustrato no varía más con el potencial aplicado, por lo cual la capacidad resultante es solo la del óxido.

$$C = \begin{cases} C'_{ox} & en \ acumulacion \\ \frac{C'_{vac}C'_{ox}}{C'_{vac}+C'_{ox}} & en \ vaciamiento \\ C'_{ox} & en \ inversion \end{cases}$$

(5.15)

Figura 5.4: Capacidad incremental de una juntura MOS N<sup>++</sup>P en función de  $v_{GB}$

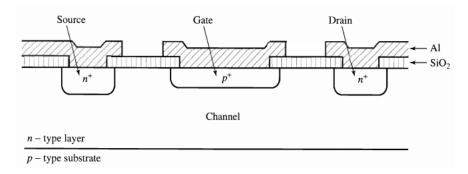

#### 6. Transistor MOSFET

La base de funcionamiento del transistor MOSFET es el canal de portadores que se forma en el régimen de inversión del capacitor MOS. En MOSFET, éste se denomina *canal de inversión*. Para poder hacer contacto con este canal, se dopan dos zonas (a ambos lados del *gate*) con dopado (fuerte) del tipo contrario al sustrato, es decir, del mismo tipo que el canal.

Una vez establecido el canal de portadores, se aplica una tensión entre los dos nuevos contactos, lo cual produce una circulación de los portadores por arrastre, debido al campo eléctrico horizontal.

Según el tipo de portadores del canal de inversión, el transistor MOS recibe el nombre de transistor de canal N o NMOS (canal de electrones); o transistor de canal P o PMOS (canal de huecos). Los contactos a ambos lados del canal reciben el nombre de source (S) y drain (D). El source se define como el contacto de partida de portadores y el drain como el contacto de llegada, cuando los mismos son arrastrados por medio del campo eléctrico horizontal.

Figura 6.1: Corte longitudinal de un transistor MOS.

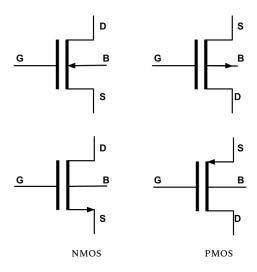

En la figura 6.2 se ilustran los símbolos utilizados para transistores MOS:

Figura 6.2: Simbología MOSFET.

#### 6.1. Principio básico de funcionamiento

El potencial entre *drain* y source debe ser tal, que las junturas (diodos) que se forman entre ellos y el sustrato estén en <u>inversa</u> en todo momento. Esto es: positiva para NMOS y negativa para PMOS. Bajo estas condiciones, la corriente de sustrato será despreciable, pudiendo considerarse nula ( $i_B \approx 0$ ).

Dado que el gate está conectado en serie con el capacitor de gate, de valor  $C_{ox}$ , la corriente de entrada de DC, en estado estacionario, será nula  $(I_G = 0)$ .

La conducción de corriente es producto del arrastre de la carga de inversión (para NMOS, electrones y para PMOS, huecos), producido por el campo eléctrico horizontal.

La magnitud de la corriente depende del producto de la velocidad de los portadores y la carga de inversión. La corriente circulando por el dispositivo tiene un valor único, que es el mismo para cada punto y a lo largo del canal. En cambio, la velocidad de los portadores y la carga de inversión, en general, experimentan variaciones a lo largo del dispositivo, pero manteniendo su producto constante.

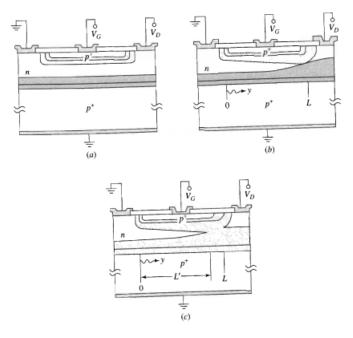

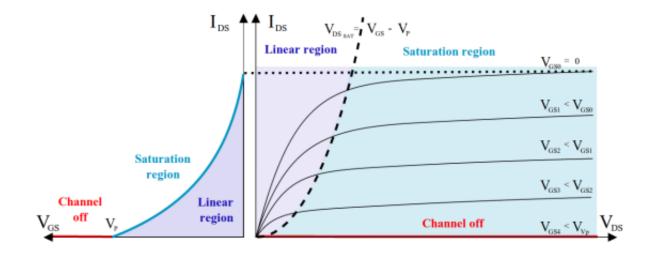

#### 6.2. Regímenes de operación

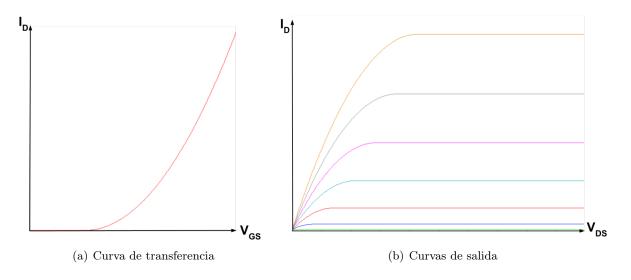

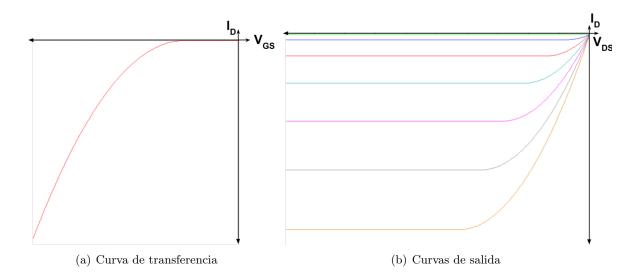

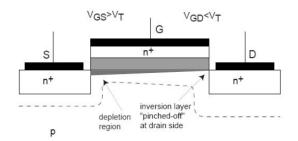

Ambos tipos de dispositivo presentan 3 regímenes posibles de operación: corte, triodo y saturación. Éstos pueden verse fácilmente con las curvas de transferencia y salida de los dispositivos.

La curva de transferencia es única para el circuito de polarización. En cambio, las curvas de salida es una para cada valor de  $V_{GS}$  (tensión aplicada entre gate y source).

#### 6.2.1. NMOS

Figura 6.3: Curvas características NMOS

#### 6.2.2. PMOS

Puede observarse en la figura 6.4 que las curvas son casi idénticas al NMOS, pero reflejadas en el tercer cuadrante.

Figura 6.4: Curvas características PMOS

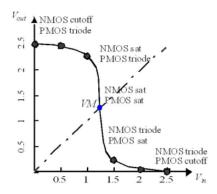

En la figura 6.8 se ilustra cómo se identifican los diferentes regímenes de operación de un MOSFET de canal N en los gráficos de las curvas características. Para un dispositivo de canal P, el análisis es análogo.

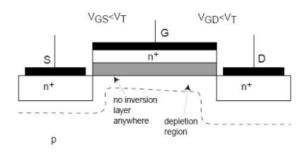

#### 6.2.3. Corte

En el régimen de corte, el transistor está "apagado", es decir que no hay corriente circulando por el mismo. Físicamente, esto se explica porque al ser la tensión aplicada en el *gate* menor a la tensión de *threshold* o *pinch-off* no se forma el canal de inversión que permite la circulación de portadores entre *source* y *drain*.

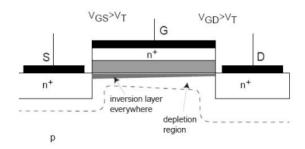

Figura 6.5: Régimen de corte

#### 6.2.4. Triodo

También llamado régimen lineal porque en este modo de operación, la relación entre la corriente de drain y la tensión drain-source es lineal. En este régimen, el gate está "activado" y la diferencia de potencial entre drain y source es pequeña, pero suficiente para que haya flujo de portadores, formando el canal de inversión. Se establece una corriente  $I_D$ . A medida que la diferencia de potencial aumenta, la corriente es cada vez mayor.

Figura 6.6: Régimen de triodo

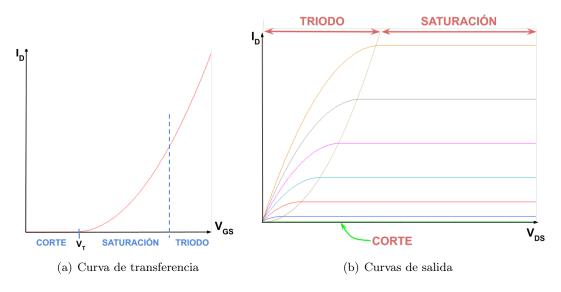

#### 6.2.5. Saturación

La corriente continúa aumentando, al igual que la tensión  $V_{DS}$ , y en consecuencia, la tensión  $V_{GD}$  disminuye, hasta pasar el límite de  $V_T$ . A partir de este momento, la corriente es independiente de la diferencia de potencial entre los terminales drain y source:  $I_D = I_{D_{sat}}$ .

En este régimen, el canal se encuentra "estrangulado" (pinched-off) en la zona del drain. Esto genera que haya una libre circulación de portadores hacia el drain (como en dos tanques de agua que están a alturas muy diferentes).

Figura 6.7: Régimen de saturación

Figura 6.8: Regímenes de operación NMOS

$$V_{DS_{sat}} = V_{GS} - V_T$$

• Canal N:

$$\text{Corte:} \qquad \left\{ \begin{array}{l} V_{GS} < V_T \\ I_D = 0 \end{array} \right.$$

$$\circ \text{ Triodo:} \qquad \left\{ \begin{array}{l} V_{GS} > V_T \\ V_{DS} < V_{DS_{sat}} \\ I_D = \mu_n C_{ox}' \frac{W}{L} \left( V_{GS} - V_T - \frac{V_{DS}}{2} \right) V_{DS} \end{array} \right.$$

$$\circ \text{ Saturación:} \left\{ \begin{array}{l} V_{GS} > V_T \\ V_{DS} > V_{DS_{sat}} \\ I_D = \frac{\mu_n C_{ox}' W}{2} \frac{W}{L} \left( V_{GS} - V_T \right)^2 \left[ 1 + \lambda (V_{DS} - V_{DS_{sat}}) \right] \right.$$

$$\left. V_T = V_{FB} - 2\phi_p + \gamma \sqrt{-\phi_p - V_{BS}} \right.$$

$$(6.1)$$

#### • Canal P:

o Corte:

$$\begin{cases} V_{GS} > V_T \\ I_D = 0 \end{cases}$$

$$\circ \text{ Triodo:} \begin{cases} V_{GS} < V_T \\ V_{DS} > V_{DS_{sat}} \\ I_D = -\mu_n C'_{ox} \frac{W}{L} \left( V_{GS} - |V_T| - \frac{V_{DS}}{2} \right) V_{DS} \end{cases}$$

$$\circ \text{ Saturación:} \begin{cases} V_{GS} < V_T \\ V_{DS} < V_{DS_{sat}} \\ I_D = -\frac{\mu_n C'_{ox}}{2} \frac{W}{L} \left( V_{GS} - V_T \right)^2 \left[ 1 - \lambda (V_{DS} - V_{DS_{sat}}) \right] \end{cases}$$

$$V_T = V_{FB} - 2\phi_n - \gamma \sqrt{\phi_n + V_{BS}}$$

$$(6.2)$$

En general, la tensión bulk - source  $V_{BS}$  es cero, pues estos dos terminales están conectados entre sí (usualmente, internamente por lo que los dispositivos vienen con 3 terminales de conexión).

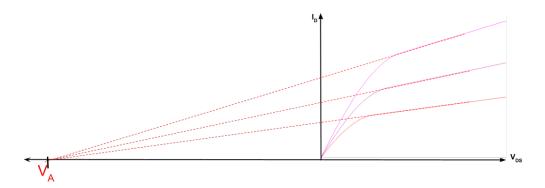

#### 6.3. Efecto de modulación del largo del canal

En realidad, a partir del voltaje de saturación la corriente no es constante, sino que esto es una aproximación (en general buena).

La modulación del largo del canal se produce por el aumento del ancho de la zona de vaciamiento en el *drain* a medida que se incrementa el voltaje. Esto conlleva a un canal de longitud más corta y una corriente de *drain* mayor. En la figura 6.9 se muestra un ejemplo algo exagerado de esto.

El efecto de modulación del largo del canal generalmente se incrementa en dispositivos pequeños con sustratos poco dopados. Un caso extremo de este efecto es *punch through*, donde el largo del canal se reduce a cero.

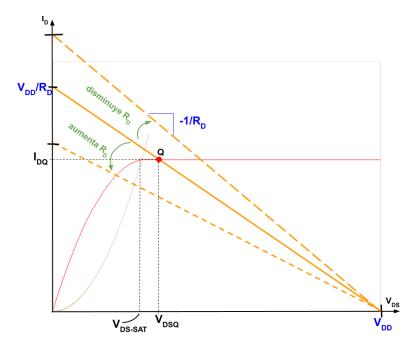

#### 6.4. Recta de carga

La recta de carga de un circuito de polarización se obtiene resolviendo la malla de salida (la que pasa por *drain* y *source*). Con esta recta puede verse en qué lugar se encuentra el punto de operación (también llamado *punto Q*) y cómo varía al variar la resistencia en el *drain*.

Figura 6.9: Efecto de modulación del largo del canal

Figura 6.10: Recta de carga de un NMOS

# 6.5. Pasos para resolver circuitos con MOSFET

- Polarización  $(V_{DS_Q}, V_{GS_Q}, I_{D_Q})$

- 1. Pasivo fuentes de señal (si las hay).

- 2. Considero todos los capacitores como <u>circuitos abiertos</u>.

- 3. Planteo corrientes y tensiones del circuito (no importa como, lo importante es respetar las convenciones durante toda la resolución).

- 4. Obtengo las expresiones de las mallas que lo componen.

- 5. Supongo régimen de saturación.

- 6. Resuelvo

- 7. Verifico si es correcta la suposición de saturación (verificando que cumpla las condiciones).

- 8. Si la suposición fue errónea vuelvo al punto 6 hasta encontrar un resultado acorde a la suposición.

- <u>Circuito</u> de pequeña señal

- o Hallo el modelo de pequeña señal.

- o Pasivo fuentes de continua.

- o Considero todos los capacitores como <u>cortocircuitos</u>.

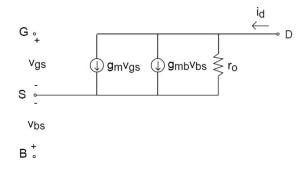

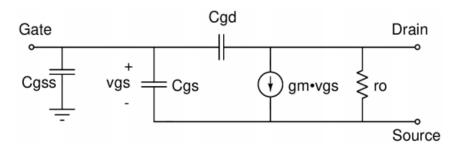

# 6.6. Modelo de pequeña señal

El modelo de pequeña señal es válido (el mismo) tanto para transistores de canal N como de canal P.

Para bajas frecuencias, las capacidades que puedan aparecer no afectan al funcionamiento, así que no se consideran.

Figura 6.11: MPS para frecuencias bajas

### 6.6.1. Transconductancia $g_m$

$$g_m = \left. \frac{\partial I_D}{\partial V_{GS}} \right|_Q \tag{6.3}$$

# 6.6.2. Resistencia de salida $r_0$

$$g_0 = \frac{\partial I_D}{\partial V_{DS}} \Big|_{Q}$$

$$r_0 = \frac{1}{g_0}$$

(6.4)

# 6.6.3. Transconductancia de $backgate g_{mb}$

Para resolver esto, es necesario escribir  $I_D$  reemplazando  $V_T$  por las ecuaciones 6.1 y 6.2 según corresponda.

$$g_{mb} = \left. \frac{\partial I_D}{\partial V_{BS}} \right|_Q \tag{6.5}$$

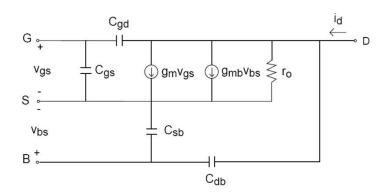

Para frecuencias altas, los efectos capacitivos de las junturas deben ser considerados, porque para estas frecuencias no se puede despreciar los efectos que ellos producen.

Figura 6.12: MPS para frecuencias altas

# 6.6.4. Capacidad de gate contra canal de inversión

$$C_{gs} = \frac{\partial Q_G}{\partial V_{GS}} \bigg|_{Q} = \frac{2}{3} W L C'_{ox} + W C_{ov}$$

$$\tag{6.6}$$

\* $W \cdot L$  es el área del gate.

La capacidad de  $overlap\ C_{ov}$  es un parámetro provisto por el fabricante y suele estar expresado en unidades de capacidad/longitud.

# 6.6.5. Capacidad gate - drain

$$C_{gd} = \frac{\partial Q_G}{\partial V_{GD}}\Big|_Q = WC_{ov} \tag{6.7}$$

# 6.6.6. Capacidad body - source

$$C_{sb} = \frac{\partial Q_G}{\partial V_{SB}} \Big|_{Q} = C'_{j} A_{S} \tag{6.8}$$

# 6.6.7. Capacidad body - drain

$$C_{db} = \frac{\partial Q_G}{\partial V_{DB}} \Big|_{Q} = C'_{j} A_D \tag{6.9}$$

# 6.6.8. Rango de validez del MPS

$$|v_{gs}| < \frac{|V_{GS} - V_T|}{5} \tag{6.10}$$

# 7. Transistor JFET

La zona de vaciamiento de una juntura p<br/>n puede ser variada a través de una tensión inversa de polarización aplicada en la juntura. Este dispositivo hace uso de este mecanismo para controlar la corriente a través de una región delimitada por dos junturas p<br/>n (entre la capa levemente dopada y el sustrato, y entre esta capa y la difusión de <br/>gate). Dado que fluye muy poca corriente a través de una juntura p<br/>n polarizada en inversa, poca potencia es consumida por el electrodo de control, mientras que bastante potencia puede ser entregada por la corriente controlada. El dispositivo puede usarse, por lo tanto, como amplificador de potencia.

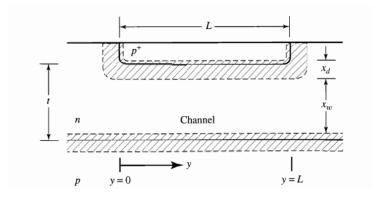

Figura 7.1: Estructura de un N-JFET.

El source provee la mayoría de portadores al canal. En consecuencia, por convención la corriente fluye de drain a source en un JFET de canal N. Si el tipo de dopado se cambia en todas las regiones de la estructura en la figura 7.1, el dibujo representará un JFET de canal P. En el dispositivo de canal P, la corriente fluye de source a drain.

La juntura p<br/>n sobre el canal sirve de elemento de control cuando se le polariza en inversa la región<br/> tipo P, llamada gate. El canal se define como una región neutral delimitada por encima por la región de<br/> vaciamiento alrededor del gate y por debajo por la región de vaciamiento alrededor de la juntura p<br/>n del sustrato. El sustrato suele estar a potencial de ground. Si el drain del JFET de canal N es polarizado<br/> positivamente, la corriente fluye de él hacia el source a través del canal. Si ahora se conecta el source<br/> a ground y se aplica un voltaje negativo al gate, la zona de vaciamiento de la juntura se ensancha y el<br/> canal se hace más angosto. Mientras que el canal se angosta, su resistencia aumenta y menos corriente<br/> fluye de drain a source. De esta manera, un voltaje aplicado en el gate controla la corriente que fluye<br/> a través del canal.

# 7.1. Análisis del dispositivo

Figura 7.2: N-JFET

Si asumimos que el potencial a lo largo del canal no cambia:

$$x_d = \sqrt{\frac{2\epsilon_{Si}}{qN_d}(\phi_B - V_G)} \tag{7.1}$$

$$I_D = G_0 \left( 1 - \sqrt{\frac{2\epsilon_{Si}}{qN_d t^2} (\phi_B - V_G)} \right) V_D \tag{7.2}$$

$$G_0 = \frac{W}{L} q \mu_n N_d t \tag{7.3}$$

Para tensiones pequeñas, el JFET se comporta como una resistencia cuya resistividad está controlada por  $V_G$ .

Si ahora la tensión aplicada no es pequeña, la tensión entre gate y el canal es función de la posición y.

$$x_d = \sqrt{\frac{2\epsilon_{Si}}{qN_d}(\phi_B - V_G + \phi(y))}$$

(7.4)

$$I_D = G_0 \left( V_D - \frac{2}{3} \left( \frac{2\epsilon_{Si}}{qN_d t^2} \right)^{1/2} \left[ (\phi_B - V_G + V_D)^{3/2} - (\phi_B - V_G)^{3/2} \right] \right)$$

(7.5)

Si la caída de tensión es muy grande, puede ser que en x=L se haga  $x_w=0$ , lo que ocurrirá cuando:

$$V_D = V_{D_{sat}} = \frac{qN_d t^2}{2\epsilon_{G}} - (\phi_B - V_G)$$

(7.6)

Con una corriente:

$$I_{D_{sat}} = G_0 \left[ \frac{qN_d t^2}{6\epsilon_{S_i}} - (\phi_B - V_G) \left( 1 - \frac{2}{3} \sqrt{\frac{2\epsilon_{S_i} (\phi_B - V_G)}{qN_d t^2}} \right) \right]$$

(7.7)

Y el resultado será:

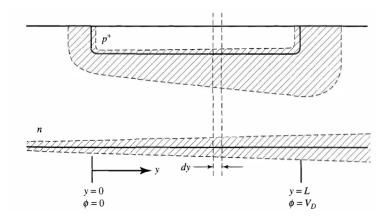

Figura 7.3: JFET en saturación

Si la SCR se extiende a lo largo de todo el alto del canal (t), la corriente se anula. Esto ocurre cuando:

$$V_G = V_P = \phi_B - \frac{qN_d t^2}{2\epsilon_{Si}} \tag{7.8}$$

$V_P$  es la tensión de umbral.

# 7.2. Regimenes del JFET

Figura 7.4: Curvas características del JFET

En el caso del JFET, el tipo (N o P) está dado por el tipo de dopaje del canal.

### • Canal N:

$$\begin{array}{l} \circ \text{ Corte:} & \left\{ \begin{array}{l} V_{GS} < V_P < 0 \\ I_D = 0 \end{array} \right. \\ \circ \text{ Triodo:} & \left\{ \begin{array}{l} V_P < V_{GS} < 0 \\ V_{DS} < V_{GS} - V_P \\ I_D = \frac{2I_{Dss}}{V_P^2} \left( V_G - V_P - \frac{V_{DS}}{2} \right) V_{DS} \end{array} \right. \\ \circ \text{ Saturación:} & \left\{ \begin{array}{l} V_P < V_{GS} < 0 \\ V_{DS} > V_{GS} - V_P \\ I_D = I_{Dss} \left( 1 - \frac{V_G}{V_P} \right)^2 \end{array} \right. \end{array}$$

### • Canal P:

Donde:

$$I_{Dss} = \frac{G_0 V_P^2}{4(\phi_R - V_P)} = \frac{1}{2} \mu \frac{\epsilon_{Si}}{t} \frac{W}{L} V_P^2$$

(7.9)

Si se considera la modulación de longitud de canal, hay que multiplicar por  $1 + \lambda (V_{DS} - V_{DS_{sat}})$ .

Figura 7.5: Símbolos y polarización de JFET

# 7.3. Modelo de pequeña señal

El MPS es útil solo en el régimen de saturación.

Figura 7.6: Modelo de pequeña señal de JFET

$$g_m = -\frac{2I_{Dss}}{V_P} \left( 1 - \frac{V_{GS}}{V_P} \right) \tag{7.10}$$

$$r_0 = \frac{1}{\lambda I_D} \tag{7.11}$$

Efectos capacitivos:

Las capacidades presentes en el JFET son debido a las junturas PN polarizadas en inversa y pueden modelizarse con las siguientes expresiones:

$$C_{gs} = \frac{C_{gs0}}{\left(1 + \frac{V_{GS}}{\phi_0}\right)^{1/3}} \tag{7.12}$$

$$C_{gd} = \frac{C_{gd0}}{\left(1 + \frac{V_{GD}}{\phi_0}\right)^{1/3}} \tag{7.13}$$

En caso de los dispositivos fabricados con tecnología planar (para integración monolítica) existe además una capacidad entre el gate y el sustrato:

$$C_{gss} = \frac{C_{gss0}}{\left(1 + \frac{V_{Gss}}{\phi_0}\right)^{1/3}} \tag{7.14}$$

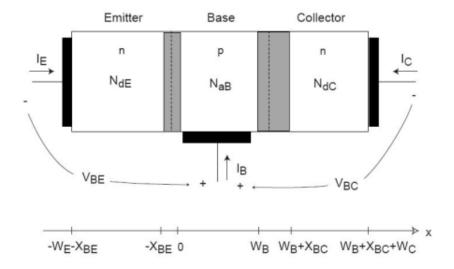

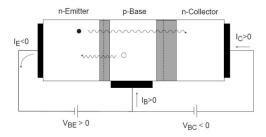

# 8. Transistor TBJ

Constructivamente, un transistor bipolar se logra disponiendo un material con un tipo de dopado entre dos materiales del dopado opuesto. La región intermedia de semiconductor dopado se denomina base y las regiones de dopado opuesto, dispuestas a ambos lados de la base, de denominan emisor y colector. El transistor se denomina de acuerdo al tipo de dopado de estas tres regiones:

- NPN (base tipo P, colector y emisor tipo N)

- PNP (base tipo N, colector y emisor tipo P)

Figura 8.1: Estructura básica de un NPN

En ambos casos, el principio de funcionamiento es el mismo. La juntura resultante entre la base y el emisor se polariza en conducción directa mediante una fuente de tensión externa, lo cual provoca una inyección de los portadores mayoritarios del emisor hacia la base. Por otro lado, la juntura base colector se polariza en inversa mediante una tensión entre sus terminales. La base se diseña lo suficientemente delgada como para que los portadores inyectados desde el emisor, que en la base son minoritarios, no se recombinen y alcancen la zona de vaciamiento de la juntura en inversa, en la cual son arrastrados por el campo eléctrico hacia el colector.

En el caso de un transistor **PNP**, se inyectan huecos del emisor a la base, los cuales continúan casi en su mayoría hacia el colector<sup>8</sup>. También se inyectan electrones de la base al emisor, que son recogidos por la fuente de alimentación. EL transistor bipolar PNP se construye de forma que la corriente de electrones de base a emisor sea muy pequeña. Como resultado, en este dispositivo se produce una corriente significativa de huecos que van de emisor a colector y una corriente muy pequeña de electrones que entran por la base y salen por el emisor.

En el caso de un transistor **NPN**, se inyectan electrones del emisor a la base, los cuales continúan casi en su mayoría hacia el colector. También se inyectan huecos de la base al emisor, que son recogidos por la fuente de alimentación. El transistor NPN se construye para que la corriente de huecos de la base al emisor sea muy pequeña.

En ambos dispositivos el efecto es el mismo y consiste en la posibilidad de controlar el flujo de corriente entre emisor y colector, mediante una pequeña corriente de base.

<sup>&</sup>lt;sup>8</sup>Efecto transistor

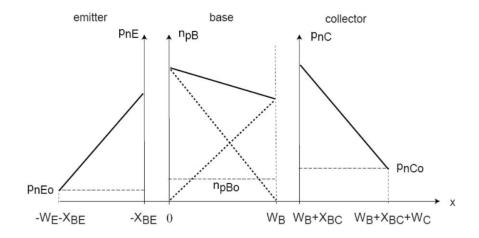

Figura 8.2: Concentración de portadores de un transistor NPN en equilibrio térmico

# 8.1. Regímenes de operación

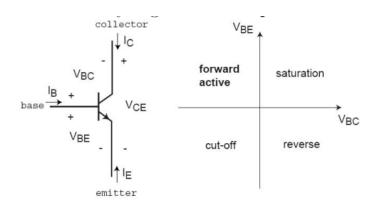

Figura 8.3: Regímenes de operación de un transistor NPN

- Modo activo directo (forward active): la corriente de colector de controla a través de  $V_{BE}$  u y tiene poca dependencia con la tensión de colector (buena aislación).

- Saturación (saturation): el TBJ está en conducción pero la corriente depende de  $V_{BE}$  y de  $V_{BC}$ . La base está inundada de portadores minoritarios.

- Reversa (reverse): ganancia es pobre; el dispositivo NO es útil en esta región y debe evitarse.

- Corte (cut-off): corrientes  $I_C$  e  $I_B$  despreciables, se encuentra en "bloqueo".

| Regimenes  | Juntura |         |

|------------|---------|---------|

| Regimenes  | BE      | ВС      |

| Corte      | Inversa | Inversa |

| Reversa    | Inversa | Directa |

| MAD        | Directa | Inversa |

| Saturación | Directa | Directa |

Cuadro 8.1: Junturas

| Comparación con el M | IOSFET: |

|----------------------|---------|

|----------------------|---------|

| Característica                  | MOSFET ideal<br>Saturación | TBJ ideal<br>MAD |  |

|---------------------------------|----------------------------|------------------|--|

| Terminal de control             | gate                       | base             |  |

| Dependencia de la               | cuadrática                 | exponencial      |  |

| corriente con la tensión        | Cuadranca                  | exponenciai      |  |

| Corriente de entrada en         | 0                          | exponencial      |  |

| continua al terminal de control | 0                          | exponencial      |  |

Cuadro 8.2: Saturación $_{MOSFET} = MAD_{TBJ}$ Triodo $_{MOSFET} = Saturación_{TBJ}$

# 8.1.1. Régimen activo directo (MAD)

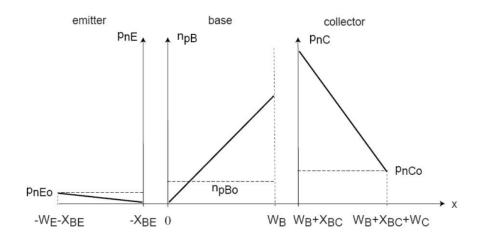

Figura 8.4: Circulación de portadores de un NPN en MAD

Figura 8.5: Perfil de portadores minoritarios de un NPN en MAD

# Para NPN:

$$I_C = I_S \exp \frac{V_{BE}}{V_{th}} \tag{8.1}$$

Corriente de emisor:

$$I_E = -I_C - I_B \tag{8.2}$$

$$\beta_F = \frac{D_{n_B} N_{d_E} W_E}{D_{p_E} N_{a_B} W_B} \tag{8.3}$$

Para PNP:

$$I_C = -I_S \exp \frac{-V_{BE}}{V_{th}} \tag{8.4}$$

Corriente de emisor:

$$I_E = -I_C - I_B \tag{8.5}$$

$$\beta_F = \frac{D_{p_B} N_{a_E} W_E}{D_{n_E} N_{d_B} W_B} \tag{8.6}$$

$I_S \equiv$  corriente de saturación del colector [A]

La **ganancia de corriente**  $\beta_F$  interesa que sea lo más grande posible. Para lograrlo, deben suceder dos cosas:

- 1. Dopar el emisor en mayor medida que la base. De esta manera, la corriente de base será pequeña respecto a las otras dos.

- Hacer la base angosta. Esto hace que el perfil de portadores de la base sea más pronunciado, provocando una mayor corriente de difusión. Por otro lado, esto evita la recombinación de portadores.

El término  $D_p/D_n$  para la expresión del transistor PNP, es menor a uno, producto de la menor difusividad y/o movilidad de los huecos con respecto a los electrones. Dado que en el transistor PNP la corriente principal es de huecos,  $\beta_F$  será menor que en los transistores NPN.

$$\beta_F \triangleq \frac{I_C}{I_B} \tag{8.7}$$

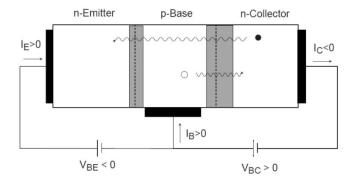

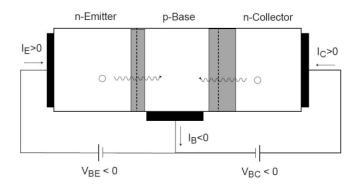

### 8.1.2. Régimen de reversa

No interesa demasiado este régimen de operación. Tiene una ganancia de corriente muy pequeña y no es lineal.

Figura 8.6: Circulación de portadores de un NPN en reversa

Figura 8.7: Perfil de portadores minoritarios de un NPN en reversa

# 8.1.3. Régimen de corte

Figura 8.8: Circulación de portadores de un NPN en corte

### Para un **NPN**:

• La base extrae huecos del emisor:

$$I_E = \frac{I_S}{\beta_F} \tag{8.8}$$

• La base extrae huecos del colector:

$$I_C = \frac{I_S}{\beta_R} \tag{8.9}$$

• La corriente de base es:

$$I_B = -I_C - I_B (8.10)$$

Estas son solo pequeñas corrientes de fuga (del orden de los pA) que en la mayoría de las aplicaciones prácticas pueden despreciarse.

Figura 8.9: Perfil de portadores minoritarios de un NPN en corte

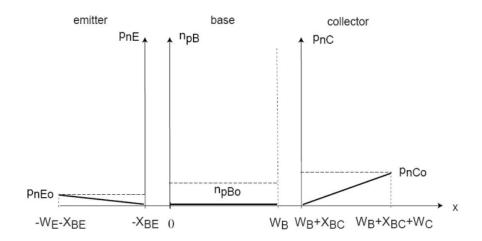

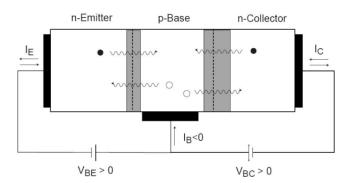

# 8.1.4. Régimen de saturación

Figura 8.10: Circulación de portadores de un NPN en saturación

El régimen de saturación es la superposición del régimen activo y el reverso.

$$I_C = I_S \left( \exp \frac{V_{BE}}{V_{th}} - \exp \frac{V_{BC}}{V_{th}} \right) - \frac{I_S}{\beta_R} \left( \exp \frac{V_{BC}}{V_{th}} - 1 \right)$$

(8.11)

$$I_B = \frac{I_S}{\beta_F} \left( \exp \frac{V_{BE}}{V_{th}} - 1 \right) + \frac{I_S}{\beta_R} \left( \exp \frac{V_{BC}}{V_{th}} - 1 \right)$$

$$(8.12)$$

$$I_E = -\frac{I_S}{\beta_F} \left( \exp \frac{V_{BE}}{V_{th}} - 1 \right) - I_S \left( \exp \frac{V_{BE}}{V_{th}} - \exp \frac{V_{BC}}{V_{th}} \right)$$

(8.13)

$I_C$  e  $I_E$  pueden tener cualquier signo, dependiendo de la magnitud relativa de  $V_{BE}$  y  $_{BC}$ , y  $\beta_F$  y  $\beta_R$ .

En saturación el colector y la base están inundados de portadores minoritarios en exceso, por lo que demora mucho sacar al dispositivo de este régimen.

Figura 8.11: Perfil de portadores minoritarios de un NPN en saturación

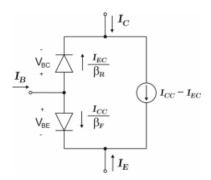

### 8.2. Modelo de Ebers Moll

Las ecuaciones que describen la operación del TBJ son 8.11, 8.12 y 8.13. Hay tres parámetros en este modelo:  $I_S$ ,  $\beta_F$  y  $\beta_R$ .

Figura 8.12: Modelo circuital de Ebers Moll

Donde:

$$I_{CC} = I_S \left( \exp \frac{V_{BE}}{V_{th}} - 1 \right) \tag{8.14}$$

$$I_{EC} = I_S \left( \exp \frac{V_{BC}}{V_{th}} - 1 \right) \tag{8.15}$$

Y típicamente  $\beta_R \simeq 0.1 - 5 \ll \beta_F$

Las curvas características y recta de carga del TBJ son muy similares a las del MOSFET.

Para resolver los problemas de polarización, los pasos a seguir son los mismos que en MOSFET, excepto que en lugar de suponer saturación, se supone MAD (el régimen equivalente a saturación en MOSFET).

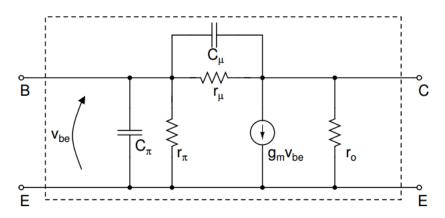

# 8.3. Modelo de pequeña señal

Este modelo será valido para  $v_{be} < 10mV$

Figura 8.13: Modelo híbrido  $\pi$

### 8.3.1. Transconductancia de salida

$$g_m = \left. \frac{\partial i_C(v_{BE})}{\partial v_{BE}} \right|_{v_{BE} = V_{BE}} = \frac{I_{CQ}}{V_{th}}$$

(8.16)

# 8.3.2. Resistencia de entrada

$$r_{\pi} = \left( \frac{\partial i_B(v_{BE})}{\partial v_{BE}} \Big|_{v_{BE} = V_{BE}} \right)^{-1} = \frac{\beta}{g_m}$$

(8.17)

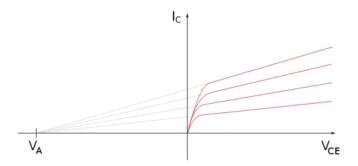

### 8.3.3. Resistencia de salida

$$r_0 = \left( \frac{\partial i_C(v_{BE}, v_{CE})}{\partial v_{CE}} \Big|_{v_{BE}, v_{CE}} \right)^{-1} \simeq \frac{V_A}{I_{CQ}}$$

(8.18)

$V_A$  es la tensión de Early.

# 8.3.4. Resistencia de realimentación

$$r_{\mu} = \left(\frac{\partial i_B}{\partial v_{BC}}\right)^{-1} = \beta r_0 \tag{8.19}$$

Tiene un valor muy elevado y generalmente puede despreciarse.

### 8.3.5. Capacidad de carga de la base

Al igual que en el caso del diodo, cuando el transistor se halla en conducción directa, su juntura EB se halla en directa y se produce una acumulación de portadores minoritarios a ambos lados de la misma. Dado que el dopado del emisor es mucho mayor que el de la base, solo es necesario considerar

la carga acumulada en la base. Una variación de la tensión  $v_{EB}$  provocará un cambio en la carga acumulada, dando lugar a un efecto capacitivo.

$$C_B = g_m \tau_F \tag{8.20}$$

El tiempo de tránsito  $\tau_F$  es el tiempo promedio que tardan los huecos en recorrer la base. Este parámetro determina la máxima velocidad de operación del transistor.

$$\tau_F \triangleq \frac{W_B^2}{2D_{p_B}} \tag{8.21}$$

Para el modelo de pequeña señal se definen dos capacidades:

$$C_{\pi} \triangleq C_{jEB} + C_B \tag{8.22}$$

$$C_{\mu} \triangleq C_{jCB} \tag{8.23}$$

Con las capacidades de juntura definidas igual que en el diodo pn (multiplicadas por el área de la juntura correspondiente).

# 8.4. Efecto de modulación del ancho de la base

Figura 8.14: Tensión de Early en un NPN

Ver apunte "TBJ - Tensión de Early"  $^{[2]}.$

# 9. Amplificadores

El objetivo es convertir potencia de la fuente de alimentación en potencia de señal de salida, amplificación de señal.

Principales características:

- La señal de salida es una réplica sin distorsión de la señal de entrada.

- El amplificador debe tener relación lineal de transferencia entrada salida.

# 9.1. Parámetros de un amplificador

Estos parámetros son inherentes al amplificador y no dependen de lo que se conecte a él.

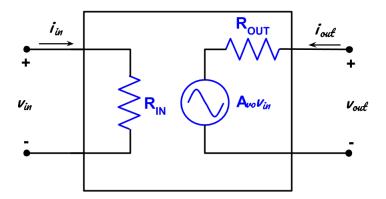

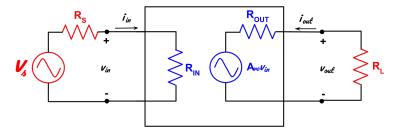

Figura 9.1: Parámetros de un amplificador

### 9.1.1. Ganancia de tensión

Es la ganancia de tensión a *circuito abierto*, es decir, sin conectar nada a la salida, y se define como la relación entre la tensión de salida y la de entrada:

$$A_{vo} = \frac{v_{out}}{v_{in}} \tag{9.1}$$

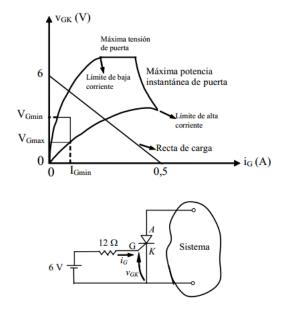

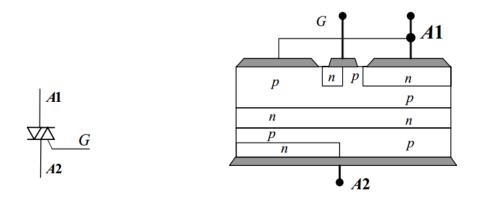

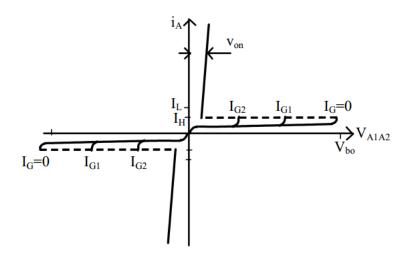

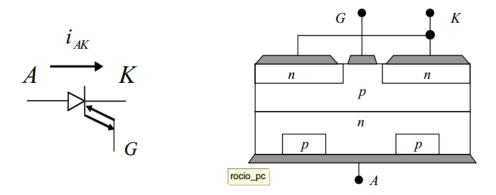

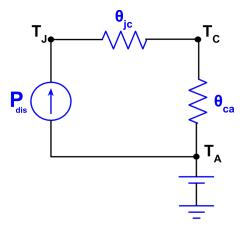

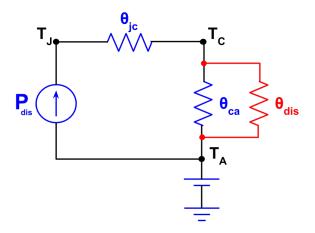

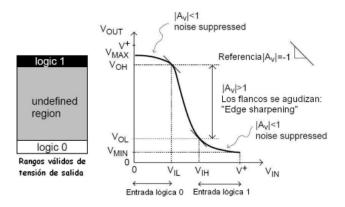

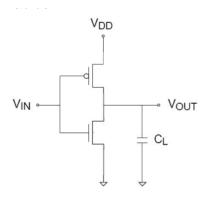

# 9.1.2. Resistencia de entrada